## SONET/SDH PRECISION CLOCK MULTIPLIER IC

#### **Features**

- Ultra-low jitter clock output with jitter generation as low as 0.3 ps<sub>RMS</sub>

- No external components (other than a resistor and bypassing)

- Input clock ranges at 19, 39, 78, 155, 311, or 622 MHz

- Output clock ranges at 19, 39, 78, 155,

311, 622, 1244, or 2488 MHz

- Maximum range includes 693 MHz for 10 GbE FEC support

- Digital hold for loss-of-input clock

- Support for 255/238 (15/14),

255/237 (85/79), and 66/64 FEC scaling (ITU-T G.709 and IEEE 802.3ae)

- Selectable loop bandwidth

- Loss-of-signal alarm output

- Low power

- Small size (9 x 9 mm)

- Maximum range includes 693 MHz for Backwards compatible with Si5320

#### **Applications**

- SONET/SDH line/port cards

- Terabit routers

- Core switches

- Digital cross connects

#### **Description**

The Si5321 is a precision clock multiplier that exceeds the requirements of high-speed communication systems, including OC-192/OC-48 and 10 Gigabit Ethernet. This device phase locks to an input clock in the 19, 39, 78, 155, 311 or 622 MHz frequency range and generates a frequency-multiplied clock output that can be configured for operation in the 19, 39, 78, 155, 622, 1244, or 2488 MHz frequency range. Silicon Laboratories DSPLL® technology provides PLL functionality with unparalleled performance. It eliminates external loop filter components, provides programmable loop parameters, and simplifies design. FEC rates are supported by selectable forward and reverse 255/238 (15/14), 255/237 (85/79), and 66/64 (33/32) conversion factors. The ITU-T G.709 255/237 rate and the IEEE 802.3ae 66/64 rate are supported when using a 155 MHz or higher rate input clock. The performance and integration of Silicon Laboratories' Si5321 clock IC provides high-level support of the latest specifications and systems. It operates from a single 3.3 V supply.

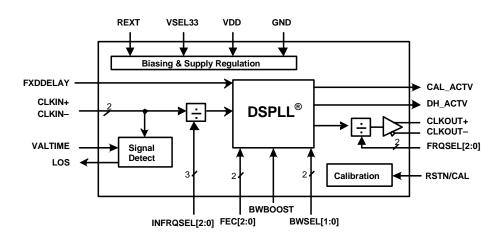

#### **Functional Block Diagram**

2

## TABLE OF CONTENTS

| SECTION                                                       | PAGE |

|---------------------------------------------------------------|------|

| 1. Electrical Specifications                                  |      |

| 2 Functional Description                                      | 17   |

| 2.1. DSPLL <sup>®</sup> · · · · · · · · · · · · · · · · · · · |      |

| 2.2. Clock Input and Output Rate Selection                    |      |

| 2.3. PLL Performance                                          |      |

| 2.4. Loss-of-Signal Alarm                                     |      |

| 2.5. Digital Hold of the PLL                                  |      |

| 2.6. Hitless Recovery from Digital Hold                       |      |

| 2.7. Reset                                                    |      |

| 2.8. PLL Self-Calibration                                     |      |

| 2.9. Bias Generation Circuitry                                |      |

| 2.10. Differential Input Circuitry                            |      |

| 2.11. Differential Output Circuitry                           |      |

| 2.12. Power Supply Connections                                |      |

| 2.13. Design and Layout Guidelines                            |      |

| 3. Pin Descriptions: Si5321                                   |      |

| 4. Ordering Guide                                             |      |

| 5. Package Outline                                            |      |

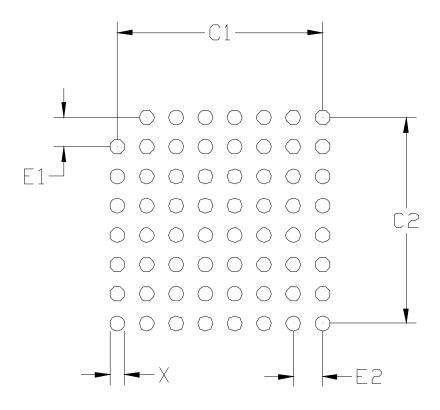

| 6. 9x9 mm PBGA Card Layout                                    |      |

| Document Change List                                          |      |

|                                                               |      |

| Contact Information                                           |      |

## 1. Electrical Specifications

**Table 1. Recommended Operating Conditions**

| Parameter                                         | Symbol            | Test Condition | Min <sup>1</sup> | Тур | Max <sup>1</sup> | Unit |

|---------------------------------------------------|-------------------|----------------|------------------|-----|------------------|------|

| Ambient Temperature                               | T <sub>A</sub>    |                | -20 <sup>2</sup> | 25  | 85               | °C   |

| Si5321 Supply Voltage <sup>3</sup> , 3.3 V Supply | V <sub>DD33</sub> |                | 3.135            | 3.3 | 3.465            | V    |

#### Notes:

- 1. All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions. Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise stated.

- 2. The Si5321 is guaranteed by design to operate at  $-40^{\circ}$  C. All electrical specifications are guaranteed for an ambient temperature of -20 to  $85^{\circ}$  C.

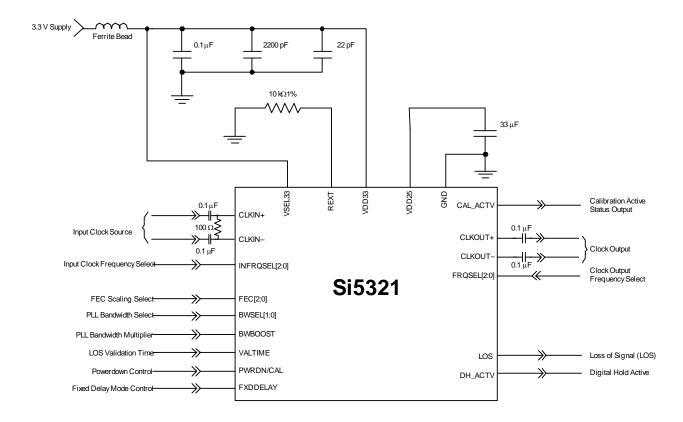

- **3.** The Si5321 specifications are guaranteed when using the recommended application circuit (including component tolerance) of Figure 5 on page 16.

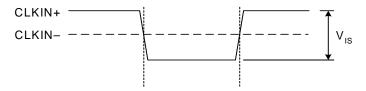

A. Operation with Single-Ended Clock Input\*

Note: When using single-ended clock sources, the unused clock input on the Si5321 must be ac-coupled to ground.

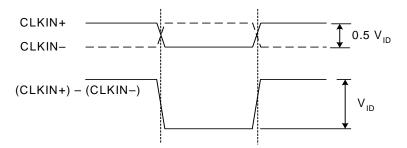

B. Operation with Differential Clock Input

Note: Transmission line termination, when required, must be provided externally.

Figure 1. CLKIN Voltage Characteristics

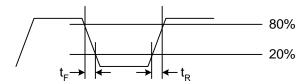

Figure 2. Rise/Fall Time Measurement

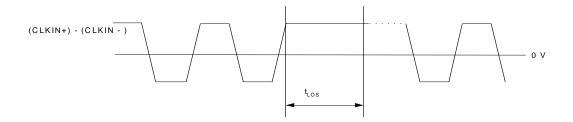

Figure 3. Transitionless Period on CLKIN for Detecting a LOS Condition

## Table 2. DC Characteristics, $V_{DD} = 3.3 \text{ V}$

(V<sub>DD33</sub> = 3.3 V  $\pm$ 5%, T<sub>A</sub> = -20 to 85 °C)

| Parameter                                                 | Symbol             | Test Condition                                          | Min | Тур | Max              | Unit             |

|-----------------------------------------------------------|--------------------|---------------------------------------------------------|-----|-----|------------------|------------------|

| Supply Current 1                                          | I <sub>DD</sub>    | 622.08 MHz In,<br>19.44 MHz Out                         | _   | 141 | 155              | mA               |

| Supply Current 2                                          | I <sub>DD</sub>    | 19.44 MHz In,<br>622.08 MHz Out                         | _   | 135 | 145              | mA               |

| Power Dissipation Using 3.3 V Supply Clock Output         | P <sub>D</sub>     | 19.44 MHz In,<br>622.08 MHz Out                         | _   | 445 | 479              | mW               |

| Common Mode Input Voltage <sup>1,2,3</sup> (CLKIN)        | V <sub>ICM</sub>   |                                                         | 1.0 | 1.5 | 2.0              | V                |

| Single-Ended Input Voltage <sup>2,3,4</sup> (CLKIN)       | V <sub>IS</sub>    | See Figure 1A                                           | 200 | _   | 500 <sup>4</sup> | $mV_{PP}$        |

| Differential Input Voltage Swing <sup>2,3,4</sup> (CLKIN) | V <sub>ID</sub>    | See Figure 1B                                           | 200 | _   | 500 <sup>4</sup> | $mV_{PP}$        |

| Input Impedance<br>(CLKIN+, CLKIN-)                       | R <sub>IN</sub>    |                                                         | _   | 80  | _                | kΩ               |

| Differential Output Voltage Swing (CLKOUT)                | V <sub>OD</sub>    | 100 $\Omega$ Load<br>Line-to-Line,<br>FRQSEL[0:2] = 011 | 750 | 825 | 1100             | mV <sub>PP</sub> |

| Output Common Mode Voltage<br>(CLKOUT)                    | V <sub>OCM</sub>   | 100 $\Omega$ Load Line-to-Line                          | 1.4 | 1.8 | 2.2              | V                |

| Output Short to GND (CLKOUT)                              | I <sub>SC(-)</sub> |                                                         | -60 | _   | _                | mA               |

| Output Short to V <sub>DD25</sub> (CLKOUT)                | I <sub>SC(+)</sub> |                                                         | _   | 15  | _                | mA               |

| Input Voltage Low (LVTTL Inputs)                          | V <sub>IL</sub>    |                                                         | _   | _   | 0.8              | V                |

| Input Voltage High (LVTTL Inputs)                         | V <sub>IH</sub>    |                                                         | 2.0 | _   | _                | V                |

| Input Low Current (LVTTL Inputs)                          | I <sub>IL</sub>    |                                                         | _   | _   | 50               | μΑ               |

| Input High Current (LVTTL Inputs)                         | I <sub>IH</sub>    |                                                         | _   | _   | 50               | μΑ               |

| Internal Pulldowns (LVTTL Inputs)                         | I <sub>pd</sub>    |                                                         |     | _   | 50               | μΑ               |

| Input Impedance (LVTTL Inputs)                            | R <sub>IN</sub>    |                                                         | 50  | _   | _                | kΩ               |

| Output Voltage Low (LVTTL Outputs)                        | V <sub>OL</sub>    | I <sub>O</sub> = 0.5 mA                                 |     | _   | 0.4              | V                |

| Output Voltage High (LVTTL Outputs)                       | V <sub>OH</sub>    | $I_{O} = 0.5 \text{ mA}$                                | 2.0 | _   | _                | V                |

#### Notes:

- 1. The Si5321 device provides weak 1.5 V internal biasing that enables ac-coupled operation.

- 2. Clock inputs may be driven differentially or single-endedly. When driven single-endedly, the unused input should be accoupled to ground.

- 3. Transmission line termination, when required, must be provided externally.

- **4.** Although the Si5321 device can operate with input clock swings as high as 1500 mV<sub>PP</sub>, Silicon Laboratories recommends maintaining the input clock amplitude below 500 mV<sub>PP</sub> for optimal performance.

**Table 3. AC Characteristics**

| Parameter                                                     | Symbol             | Test Condition                                    | Min    | Тур | Max    | Unit |

|---------------------------------------------------------------|--------------------|---------------------------------------------------|--------|-----|--------|------|

| Input Clock Frequency (CLKIN)<br>FEC[2:0] = 000 (non FEC)     | f <sub>CLKIN</sub> | No FEC Scaling,<br>FXDDELAY = 1                   |        |     |        |      |

| INFRQSEL[2:0] = 001                                           |                    |                                                   | 19.436 | _   | 21.685 |      |

| INFRQSEL[2:0] = 010                                           |                    |                                                   | 38.872 |     | 43.369 | MHz  |

| INFRQSEL[2:0] = 011                                           |                    |                                                   | 77.744 | _   | 86.738 |      |

| INFRQSEL[2:0] = 100                                           |                    |                                                   | 155.48 |     | 173.48 |      |

| INFRQSEL[2:0] = 101                                           |                    |                                                   | 310.97 | _   | 346.95 |      |

| INFRQSEL[2:0] = 110                                           |                    |                                                   | 621.95 |     | 693.90 |      |

| Input Clock Frequency (CLKIN)<br>FEC[2:0] = 001 (forward FEC) | f <sub>CLKIN</sub> | 255/238 FEC Scaling,<br>FXDDELAY = 1              |        |     |        |      |

| INFRQSEL[2:0] = 001                                           |                    |                                                   | 18.142 | _   | 20.239 |      |

| INFRQSEL[2:0] = 010                                           |                    |                                                   | 36.284 |     | 40.478 | MHz  |

| INFRQSEL[2:0] = 011                                           |                    |                                                   | 72.568 |     | 80.955 |      |

| INFRQSEL[2:0] = 100                                           |                    |                                                   | 145.13 |     | 161.91 |      |

| INFRQSEL[2:0] = 101                                           |                    |                                                   | 290.27 | _   | 323.82 |      |

| INFRQSEL[2:0] = 110                                           |                    |                                                   | 580.54 | _   | 647.64 |      |

| Input Clock Frequency (CLKIN)<br>FEC[2:0] = 010 (reverse FEC) | f <sub>CLKIN</sub> | 238/255 FEC Scaling,<br>FXDDELAY = 1              |        |     |        |      |

| INFRQSEL[2:0] = 001                                           |                    |                                                   | 20.826 |     | 23.234 |      |

| INFRQSEL[2:0] = 010                                           |                    |                                                   | 41.652 | _   | 46.465 | MHz  |

| INFRQSEL[2:0] = 011                                           |                    |                                                   | 83.305 | _   | 92.934 |      |

| INFRQSEL[2:0] = 100                                           |                    |                                                   | 166.61 | _   | 185.87 |      |

| INFRQSEL[2:0] = 101                                           |                    |                                                   | 333.22 | _   | 371.74 |      |

| INFRQSEL[2:0] = 110                                           |                    |                                                   | 666.44 | _   | 743.47 |      |

| Input Clock Frequency (CLKIN)<br>FEC[2:0] = 100 (forward FEC) | f <sub>CLKIN</sub> | 255/237 FEC Scaling<br>Minimum input frequency is |        |     |        |      |

| INFRQSEL[2:0] = 001                                           |                    | in the 155 MHz range,                             | N/A    | N/A | N/A    |      |

| INFRQSEL[2:0] = 010                                           |                    | FXDDELAY = 1                                      | N/A    | N/A | N/A    | MHz  |

| INFRQSEL[2:0] = 011                                           |                    |                                                   | N/A    | N/A | N/A    |      |

| INFRQSEL[2:0] = 100                                           |                    |                                                   | 144.52 | _   | 161.23 |      |

| INFRQSEL[2:0] = 101                                           |                    |                                                   | 289.05 | _   | 322.46 |      |

| INFRQSEL[2:0] = 110                                           |                    |                                                   | 578.11 | _   | 644.92 |      |

| Input Clock Frequency (CLKIN)                                 | f <sub>CLKIN</sub> | 237/255 FEC Scaling                               |        |     |        |      |

| FEC[2:0] = 101 (reverse FEC)                                  |                    | Minimum input frequency is                        |        |     |        |      |

| INFRQSEL[2:0] = 001                                           |                    | in the 155 MHz range,                             | N/A    | N/A | N/A    |      |

| INFRQSEL[2:0] = 010                                           |                    | FXDDELAY = 1                                      | N/A    | N/A | N/A    | MHz  |

| INFRQSEL[2:0] = 011                                           |                    |                                                   | N/A    | N/A | N/A    |      |

| INFRQSEL[2:0] = 100                                           |                    |                                                   | 167.31 | _   | 186.66 |      |

| INFRQSEL[2:0] = 101                                           |                    |                                                   | 334.62 | _   | 373.31 |      |

| INFRQSEL[2:0] = 110                                           |                    |                                                   | 669.25 | _   | 746.61 |      |

Note: The Si5321 provides a 1/32x, 1/16x, 1/8x, 1/4x, 1/2x, 1x, 2x, 4x, 8x, 16x, 32x, 64x, or 128x clock multiplication function with an option for additional frequency scaling by a factor of 255/238, 238/255, 255/237, 237/255, 66/64, or 64/66 for FEC rate conversion.

## Table 3. AC Characteristics (Continued)

$(V_{DD33} = 3.3 \text{ V } \pm 5\%, T_A = -20 \text{ to } 85 \text{ °C})$

| Parameter                                                                                                                                                                                              | Symbol                                                                                                                                                                      | Test Condition                                                                     | Min                                                                          | Тур                                  | Max                                                                          | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------|------|

| Input Clock Frequency (CLKIN) FEC[2:0] = 110 (forward FEC) INFRQSEL[2:0] = 001 INFRQSEL[2:0] = 010 INFRQSEL[2:0] = 011 INFRQSEL[2:0] = 100 INFRQSEL[2:0] = 101 INFRQSEL[2:0] = 101 INFRQSEL[2:0] = 110 | f <sub>CLKIN</sub>                                                                                                                                                          | 66/64 FEC Scaling Minimum input frequency is in the 155 MHz range, FXDDELAY = 1    | N/A<br>N/A<br>N/A<br>150.79<br>301.58<br>603.16                              | N/A<br>N/A<br>N/A<br>—<br>—          | N/A<br>N/A<br>N/A<br>168.22<br>336.44<br>672.88                              | MHz  |

| Input Clock Frequency (CLKIN) FEC[2:0] = 111 (reverse FEC) INFRQSEL[2:0] = 001 INFRQSEL[2:0] = 010 INFRQSEL[2:0] = 011 INFRQSEL[2:0] = 100 INFRQSEL[2:0] = 101 INFRQSEL[2:0] = 110                     | f <sub>CLKIN</sub>                                                                                                                                                          | 64/66 FEC Scaling Minimum input frequency is in the 155 MHz range, FXDDELAY = 1    | N/A<br>N/A<br>N/A<br>160.36<br>320.72<br>641.46                              | N/A<br>N/A<br>N/A<br>—<br>—          | N/A<br>N/A<br>N/A<br>178.90<br>357.80<br>715.59                              | MHz  |

| Input Clock Rise Time (CLKIN)                                                                                                                                                                          | t <sub>R</sub>                                                                                                                                                              | Figure 2                                                                           | _                                                                            | _                                    | 11                                                                           | ns   |

| Input Clock Fall Time (CLKIN)                                                                                                                                                                          | t <sub>F</sub>                                                                                                                                                              | Figure 2                                                                           | _                                                                            |                                      | 11                                                                           | ns   |

| Input Clock Duty Cycle                                                                                                                                                                                 | C <sub>DUTY_IN</sub>                                                                                                                                                        |                                                                                    | 40                                                                           | 50                                   | 60                                                                           | %    |

| CLKOUT Frequency Range<br>FRQSEL[2:0] = 001<br>FRQSEL[2:0] = 000<br>FRQSEL[2:0] = 100<br>FRQSEL[2:0] = 010<br>FRQSEL[2:0] = 101<br>FRQSEL[2:0] = 011<br>FRQSEL[2:0] = 110<br>FRQSEL[2:0] = 111         | f <sub>O_19</sub><br>f <sub>O_39</sub><br>f <sub>O_78</sub><br>f <sub>O_155</sub><br>f <sub>O_311</sub><br>f <sub>O_622</sub><br>f <sub>O_1250</sub><br>f <sub>O_2500</sub> |                                                                                    | 19.436<br>38.872<br>77.744<br>155.48<br>310.97<br>621.95<br>1243.9<br>2487.8 | <br> -<br> -<br> -<br> -<br> -<br> - | 21.685<br>43.369<br>86.738<br>173.48<br>346.95<br>693.90<br>1387.8<br>2775.6 | MHz  |

| CLKOUT Rise Time                                                                                                                                                                                       | t <sub>R</sub>                                                                                                                                                              | Figure 2; differential; after 3 cm of 50 $\Omega$ FR4 stripline, FRQSEL[0:2] = 011 | _                                                                            | 190                                  | 220                                                                          | ps   |

| CLKOUT Fall Time                                                                                                                                                                                       | t <sub>F</sub>                                                                                                                                                              | Figure 2; differential; after 3 cm of 50 $\Omega$ FR4 stripline, FRQSEL[0:2] = 011 | _                                                                            | 190                                  | 220                                                                          | ps   |

| Output Clock Duty Cycle                                                                                                                                                                                | C <sub>DUTY_OUT</sub>                                                                                                                                                       | Differential:<br>(CLKOUT+) - (CLKOUT-),<br>FRQSEL[0:2] = 011                       | 48                                                                           | _                                    | 52                                                                           | %    |

| RSTN/CAL Pulse Width                                                                                                                                                                                   | t <sub>RSTN</sub>                                                                                                                                                           |                                                                                    | 20                                                                           | _                                    | _                                                                            | ns   |

Note: The Si5321 provides a 1/32x, 1/16x, 1/8x, 1/4x, 1/2x, 1x, 2x, 4x, 8x, 16x, 32x, 64x, or 128x clock multiplication function with an option for additional frequency scaling by a factor of 255/238, 238/255, 255/237, 237/255, 66/64, or 64/66 for FEC rate conversion.

SILICUN

# Table 3. AC Characteristics (Continued) (V<sub>DD33</sub> = 3.3 V $\pm 5\%$ , T<sub>A</sub> = -20 to 85 °C)

| Parameter                                                                                                                                                                                            | Symbol           | Test Condition                                                                  | Min                                                                      | Тур         | Max                                                                                                                                                | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Transitionless Period Required on CLKIN for Detecting a LOS Condition.  INFRQSEL[2:0] = 001  INFRQSEL[2:0] = 010  INFRQSEL[2:0] = 011  INFRQSEL[2:0] = 100  INFRQSEL[2:0] = 101  INFRQSEL[2:0] = 101 | t <sub>LOS</sub> |                                                                                 | 24/fo_622<br>16/fo_622<br>12/fo_622<br>10/fo_622<br>9/fo_622<br>8/fo_622 | _<br>_<br>_ | 32/ <sub>fo_622</sub><br>32/ <sub>fo_622</sub><br>32/ <sub>fo_622</sub><br>32/ <sub>fo_622</sub><br>32/ <sub>fo_622</sub><br>32/ <sub>fo_622</sub> | S    |

| Recovery Time for Clearing an LOS Condition VALTIME = 0 VALTIME = 1                                                                                                                                  | t <sub>VAL</sub> | Measured from when a valid reference clock is applied until the LOS flag clears | 1.6<br>90                                                                |             | 3.2<br>220                                                                                                                                         | ms   |

Note: The Si5321 provides a 1/32x, 1/16x, 1/8x, 1/4x, 1/2x, 1x, 2x, 4x, 8x, 16x, 32x, 64x, or 128x clock multiplication function with an option for additional frequency scaling by a factor of 255/238, 238/255, 255/237, 237/255, 66/64, or 64/66 for FEC rate conversion.

**Table 4. AC Characteristics (PLL Performance Characteristics)**

| Parameter                                                            | Symbol                | Test Condition   | Min  | Тур  | Max  | Unit |

|----------------------------------------------------------------------|-----------------------|------------------|------|------|------|------|

| Wander/Jitter at 800 Hz Bandwidth (BWSEL[1:0] = 10 and BWBOOST = 0;  | FXDDELAY              | = 1)             |      |      |      |      |

| Jitter Tolerance (see Figure 7)                                      |                       | f = 8 Hz         | 1000 | _    | _    | ns   |

|                                                                      | $J_{TOL(PP)}$         | f = 80 Hz        | 100  | _    | _    | ns   |

|                                                                      |                       | f = 800 Hz       | 10   | _    | _    | ns   |

| CLKOUT RMS Jitter Generation                                         | J <sub>GEN(RMS)</sub> | 12 kHz to 20 MHz | _    | 0.9  | 1.2  | ps   |

| FEC[2:0] = 000                                                       |                       | 50 kHz to 80 MHz | _    | 0.27 | 0.35 | ps   |

| CLKOUT RMS Jitter Generation                                         | J <sub>GEN(RMS)</sub> | 12 kHz to 20 MHz | _    | 0.9  | 1.2  | ps   |

| FEC[2:0] = 001, 010, 100, 101, 110, 111                              |                       | 50 kHz to 80 MHz | _    | 0.27 | 0.35 | ps   |

| CLKOUT Peak-Peak Jitter Generation                                   | J <sub>GEN(PP)</sub>  | 12 kHz to 20 MHz | _    | 7.6  | 11   | ps   |

| FEC[2:0] = 000                                                       |                       | 50 kHz to 80 MHz | _    | 3.6  | 10.0 | ps   |

| CLKOUT Peak-Peak Jitter Generation                                   | J <sub>GEN(PP)</sub>  | 12 kHz to 20 MHz | _    | 6.7  | 9.2  | ps   |

| FEC[2:0] = 001, 010, 100, 101, 110, 111                              |                       | 50 kHz to 80 MHz | _    | 3.0  | 10.0 | ps   |

| Jitter Transfer Bandwidth (see Figure 6)                             | F <sub>BW</sub>       | BW = 800 Hz      | _    | 800  | _    | Hz   |

| Wander/Jitter Transfer Peaking                                       | J <sub>P</sub>        | < 800 Hz         | _    | 0.0  | 0.05 | dB   |

| Wander/Jitter at 1600 Hz Bandwidth (BWSEL[1:0] = 10 and BWBOOST = 1; | FXDDELAY              | = 1)             |      |      |      |      |

| Jitter Tolerance (see Figure 7)                                      |                       | f = 16 Hz        | 500  | _    |      | ns   |

|                                                                      |                       | f = 160 Hz       | 50   | _    | _    | ns   |

|                                                                      |                       | f = 1600 Hz      | 5    | _    | _    | ns   |

| CLKOUT RMS Jitter Generation                                         | J <sub>GEN(RMS)</sub> | 12 kHz to 20 MHz | _    | .80  | 1.0  | ps   |

| FEC[2:0] = 000                                                       |                       | 50 kHz to 80 MHz | _    | .25  | .30  | ps   |

| CLKOUT Peak-Peak Jitter Generation                                   | J <sub>GEN(PP)</sub>  | 12 kHz to 20 MHz | _    | 6.4  | 10.0 | ps   |

| FEC[2:0] = 000                                                       |                       | 50 kHz to 80 MHz | _    | 3.0  | 5.0  | ps   |

| Jitter Transfer Bandwidth (see Figure 6)                             | F <sub>BW</sub>       | BW = 1600 Hz     | _    | 1600 | _    | Hz   |

| Wander/Jitter Transfer Peaking                                       | J <sub>P</sub>        | < 1600 Hz        | _    | 0.0  | 0.05 | dB   |

#### Notes:

- 1. Higher PLL bandwidth settings provide smaller clock output wander with temperature gradient.

- 2. For reliable device operation, temperature gradients should be limited to 10 °C/min.

- 3. Telcordia GR-1244-CORE requirements specify maximum phase transient slope during clock rearrangement in terms of nanoseconds per millisecond. The equivalent ps/μs unit is used here since the maximum phase transient magnitude for the Si5321 (tPT\_MTIE) never reaches one nanosecond.

Table 4. AC Characteristics (PLL Performance Characteristics) (Continued)

| Parameter                                                            | Symbol                | Test Condition    | Min        | Тур  | Max      | Unit |

|----------------------------------------------------------------------|-----------------------|-------------------|------------|------|----------|------|

| Wander/Jitter at 1600 Hz Bandwidth                                   | EVDDEL AV             | 4)                |            | 1    | <u>I</u> |      |

| (BWSEL[1:0] = 01 and BWBOOST = 0;                                    |                       |                   | 1000       |      |          |      |

| Jitter Tolerance (see Figure 9)                                      | J <sub>TOL(PP)</sub>  | f = 16 Hz         | 1000       | _    |          | ns   |

|                                                                      |                       | f = 160 Hz        | 100        | _    |          | ns   |

|                                                                      |                       | f = 1600 Hz       | 10         | _    | _        | ns   |

| CLKOUT RMS Jitter Generation                                         | J <sub>GEN(RMS)</sub> | 12 kHz to 20 MHz  | _          | 8.0  | 1.2      | ps   |

| FEC[2:0] = 000                                                       |                       | 50 kHz to 80 MHz  | _          | 0.27 | 0.35     | ps   |

| CLKOUT RMS Jitter Generation                                         | J <sub>GEN(RMS)</sub> | 12 kHz to 20 MHz, | _          | 0.9  | 1.2      | ps   |

| FEC[2:0] = 001, 010, 100, 101, 110, 111                              |                       | 50 kHz to 80 MHz, | _          | 0.27 | 0.35     | ps   |

| CLKOUT Peak-Peak Jitter Generation                                   | J <sub>GEN(PP)</sub>  | 12 kHz to 20 MHz, | _          | 6.7  | 10.0     | ps   |

| FEC[2:0] = 000                                                       |                       | 50 kHz to 80 MHz, | _          | 3.0  | 5.0      | ps   |

| CLKOUT Peak-Peak Jitter Generation                                   | J <sub>GEN(PP)</sub>  | 12 kHz to 20 MHz, | _          | 6.5  | 10.0     | ps   |

| FEC[2:0] = 001, 010, 100, 101, 110, 111                              |                       | 50 kHz to 80 MHz, | T —        | 3.0  | 5.0      | ps   |

| Jitter Transfer Bandwidth (see Figure 6)                             | F <sub>BW</sub>       | BW = 1600 Hz      | _          | 1600 | _        | Hz   |

| Wander/Jitter Transfer Peaking                                       | J <sub>P</sub>        | < 1600 Hz         | _          | 0.0  | 0.1      | dB   |

| Wander/Jitter at 3200 Hz Bandwidth (BWSEL[1:0] = 01 and BWBOOST = 1; | FXDDELAY              | = 1)              |            |      |          |      |

| Jitter Tolerance (see figure 7)                                      |                       | f = 32 Hz         | 500        | _    | _        | ns   |

|                                                                      |                       | f = 320 Hz        | 50         | _    | _        | ns   |

|                                                                      |                       | f = 3200 Hz       | 5          | _    | _        | ns   |

| CLKOUT RMS Jitter Generation                                         | J <sub>GEN(RMS)</sub> | 12 kHz to 20 MHz, | _          | 0.8  | 1.0      | ps   |

| FEC[2:0] = 000                                                       |                       | 50 kHz to 80 MHz, | _          | 0.25 | 0.3      | ps   |

| CLKOUT Peak-Peak Jitter Generation                                   | J <sub>GEN(PP)</sub>  | 12 kHz to 20 MHz, | _          | 6.1  | 10.0     | ps   |

| FEC[2:0] = 000                                                       |                       | 50 kHz to 80 MHz, | <b> </b> _ | 3.0  | 5.0      | ps   |

| Jitter Transfer Bandwidth (see Figure 6)                             | F <sub>BW</sub>       | BW = 3200 Hz      | _          | 3200 |          | Hz   |

|                                                                      | 1                     |                   | 1          | l    | 1        |      |

#### Notes:

- **1.** Higher PLL bandwidth settings provide smaller clock output wander with temperature gradient.

- 2. For reliable device operation, temperature gradients should be limited to 10 °C/min.

- **3.** Telcordia GR-1244-CORE requirements specify maximum phase transient slope during clock rearrangement in terms of nanoseconds per millisecond. The equivalent ps/μs unit is used here since the maximum phase transient magnitude for the Si5321 (tPT\_MTIE) never reaches one nanosecond.

Table 4. AC Characteristics (PLL Performance Characteristics) (Continued)

| Parameter                                                              | Symbol                | Test Condition   | Min  | Тур  | Max  | Unit |

|------------------------------------------------------------------------|-----------------------|------------------|------|------|------|------|

| Wander/Jitter Transfer Peaking                                         | J <sub>P</sub>        | < 3200 Hz        | _    | 0.05 | 0.1  | dB   |

| Wander/Jitter at 3200 Hz Bandwidth (BWSEL[1:0] = 00 and BWBOOST= 0; F  | XDDELAY :             | = 1)             |      |      |      |      |

| Jitter Tolerance (see Figure 7)                                        | J <sub>TOL(PP)</sub>  | f = 32 Hz        | 1000 |      |      | ns   |

|                                                                        |                       | f = 320 Hz       | 100  | _    |      | ns   |

|                                                                        |                       | f = 3200 Hz      | 10   | _    |      | ns   |

| CLKOUT RMS Jitter Generation                                           | J <sub>GEN(RMS)</sub> | 12 kHz to 20 MHz | _    | 0.9  | 1.1  | ps   |

| FEC[2:0] = 000                                                         |                       | 50 kHz to 80 MHz | _    | 0.3  | 0.4  | ps   |

| CLKOUT RMS Jitter Generation                                           | J <sub>GEN(RMS)</sub> | 12 kHz to 20 MHz | _    | 0.85 | 1.1  | ps   |

| FEC[2:0] = 001, 010, 100,101, 110, 111                                 |                       | 50 kHz to 80 MHz | _    | 0.3  | 0.49 | ps   |

| CLKOUT Peak-Peak Jitter Generation                                     | J <sub>GEN(PP)</sub>  | 12 kHz to 20 MHz | _    | 7.1  | 10.0 | ps   |

| FEC[2:0] = 000                                                         |                       | 50 kHz to 80 MHz | _    | 3.2  | 5.0  | ps   |

| CLKOUT Peak-Peak Jitter Generation                                     | J <sub>GEN(PP)</sub>  | 12 kHz to 20 MHz | _    | 6.6  | 11.0 | ps   |

| FEC[2:0] = 001, 010, 100,101, 110, 111                                 |                       | 50 kHz to 80 MHz | _    | 3.2  | 5.5  | ps   |

| Jitter Transfer Bandwidth (see Figure 6)                               | F <sub>BW</sub>       | BW = 3200 Hz     | _    | 3200 | _    | Hz   |

| Wander/Jitter Transfer Peaking                                         | J <sub>P</sub>        | < 3200 Hz        | _    | 0.05 | 0.1  | dB   |

| Wander/Jitter at 6400 Hz Bandwidth (BWSEL[1:0] = 00 and BWBOOST = 1; I | FXDDELAY              | = 1)             |      |      |      |      |

| Jitter Tolerance (see Figure 7)                                        |                       | f = 64 Hz        | 500  | _    | _    | ns   |

|                                                                        |                       | f = 640 Hz       | 50   | _    | _    | ns   |

|                                                                        |                       | f = 6400 Hz      | 5    | _    | _    | ns   |

| CLKOUT RMS Jitter Generation                                           | J <sub>GEN(RMS)</sub> | 12 kHz to 20 MHz | _    | 0.75 | 0.95 | ps   |

| FEC[2:0] = 000                                                         |                       | 50 kHz to 80 MHz | _    | 0.27 | 0.35 | ps   |

| CLKOUT Peak-Peak Jitter Generation                                     | J <sub>GEN(PP)</sub>  | 12 kHz to 20 MHz | _    | 6.1  | 10.0 | ps   |

| FEC[2:0] = 000                                                         | , ,                   | 50 kHz to 80 MHz | _    | 3.1  | 5.0  | ps   |

| Jitter Transfer Bandwidth (see Figure 6)                               | F <sub>BW</sub>       | BW = 6400 Hz     | _    | 6400 | _    | Hz   |

| Wander/Jitter Transfer Peaking                                         | J <sub>P</sub>        | < 6400 Hz        | _    | 0.05 | 0.1  | dB   |

#### Notes:

- 1. Higher PLL bandwidth settings provide smaller clock output wander with temperature gradient.

- 2. For reliable device operation, temperature gradients should be limited to 10 °C/min.

- **3.** Telcordia GR-1244-CORE requirements specify maximum phase transient slope during clock rearrangement in terms of nanoseconds per millisecond. The equivalent ps/μs unit is used here since the maximum phase transient magnitude for the Si5321 (tPT\_MTIE) never reaches one nanosecond.

Table 4. AC Characteristics (PLL Performance Characteristics) (Continued)

| Parameter                                                             | Symbol                | Test Condition                                                        | Min  | Тур   | Max  | Unit |

|-----------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------|------|-------|------|------|

| Wander/Jitter at 6400 Hz Bandwidth (BWSEL[1:0] = 11 and BWBOOST = 0;  | FXDDELAY              | = 1)                                                                  |      |       |      |      |

| Jitter Tolerance (see Figure 7)                                       | J <sub>TOL(PP)</sub>  | f = 64 Hz                                                             | 1000 | _     | _    | ns   |

|                                                                       |                       | f = 640 Hz                                                            | 100  | _     | _    | ns   |

|                                                                       |                       | f = 6400 Hz                                                           | 10   | _     | _    | ns   |

| CLKOUT RMS Jitter Generation                                          | J <sub>GEN(RMS)</sub> | 12 kHz to 20 MHz                                                      | _    | 1.0   | 1.3  | ps   |

| FEC[2:0] = 000                                                        |                       | 50 kHz to 80 MHz                                                      | _    | 0.4   | .55  | ps   |

| CLKOUT RMS Jitter Generation                                          | J <sub>GEN(RMS)</sub> | 12 kHz to 20 MHz                                                      | _    | 1.0   | 1.5  | ps   |

| FEC[2:0] = 001, 010, 100,101, 110, 111                                |                       | 50 kHz to 80 MHz                                                      | _    | .45   | 0.7  | ps   |

| CLKOUT Peak-Peak Jitter Generation                                    | J <sub>GEN(PP)</sub>  | 12 kHz to 20 MHz                                                      | _    | 9.3   | 13.0 | ps   |

| FEC[2:0] = 000                                                        |                       | 50 kHz to 80 MHz                                                      |      | 4.1   | 6.0  | ps   |

| CLKOUT Peak-Peak Jitter Generation                                    | J <sub>GEN(PP)</sub>  | 12 kHz to 20 MHz                                                      |      | 8.0   | 20.0 | ps   |

| FEC[2:0] = 001, 010, 100,101, 110, 111                                |                       | 50 kHz to 80 MHz                                                      |      | 4.0   | 7.5  | ps   |

| Jitter Transfer Bandwidth (see Figure 6)                              | F <sub>BW</sub>       | BW = 6400 Hz                                                          | _    | 6400  | _    | Hz   |

| Wander/Jitter Transfer Peaking                                        | J <sub>P</sub>        | < 6400 Hz                                                             | _    | 0.05  | 0.1  | dB   |

| Wander/Jitter at 12800 Hz Bandwidth (BWSEL[1:0] = 11 and BWBOOST = 1; | FXDDELAY              | = 1)                                                                  |      |       |      |      |

| Jitter Tolerance (see Figure 7)                                       |                       | f = 128 Hz                                                            | 500  | _     | _    | ns   |

|                                                                       |                       | f = 1280 Hz                                                           | 50   | _     | _    | ns   |

|                                                                       |                       | f = 12800 Hz                                                          | 5    | _     | _    | ns   |

| CLKOUT RMS Jitter Generation                                          | J <sub>GEN(RMS)</sub> | 12 kHz to 20 MHz                                                      | _    | .85   | 1.2  | ps   |

| FEC[2:0] = 000                                                        |                       | 50 kHz to 80 MHz                                                      | _    | .35   | .55  | ps   |

| CLKOUT Peak-Peak Jitter Generation                                    | J <sub>GEN(PP)</sub>  | 12 kHz to 20 MHz                                                      | _    | 6.8   | 11.0 | ps   |

| FEC[2:0] = 000                                                        |                       | 50 kHz to 80 MHz                                                      | _    | 3.4   | 5.5  | ps   |

| Jitter Transfer Bandwidth (see Figure 6)                              | F <sub>BW</sub>       | BW = 12,800 Hz                                                        | _    | 12800 | _    | Hz   |

| Wander/Jitter Transfer Peaking                                        | J <sub>P</sub>        | < 12,800 Hz                                                           | _    | 0.05  | .1   | dB   |

| Acquisition Time                                                      | T <sub>AQ</sub>       | RSTN/CAL high to CAL_ACTV low, with valid clock input and VALTIME = 0 | _    | 300   | 350  | ms   |

#### Notes:

- 1. Higher PLL bandwidth settings provide smaller clock output wander with temperature gradient.

- 2. For reliable device operation, temperature gradients should be limited to 10  $^{\circ}$ C/min.

- 3. Telcordia GR-1244-CORE requirements specify maximum phase transient slope during clock rearrangement in terms of nanoseconds per millisecond. The equivalent ps/ $\mu$ s unit is used here since the maximum phase transient magnitude for the Si5321 (tPT\_MTIE) never reaches one nanosecond.

## Table 4. AC Characteristics (PLL Performance Characteristics) (Continued)

$(V_{DD33} = 3.3 \text{ V } \pm 5\%, \text{ TA} = -20 \text{ to } 85 \text{ °C})$

| Parameter                                                                                                                    | Symbol               | Test Condition                                                                          | Min              | Тур                | Max                    | Unit              |

|------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------|------------------|--------------------|------------------------|-------------------|

| Clock Output Wander with<br>Temperature Gradient <sup>1,2</sup>                                                              | C <sub>CO_TG</sub>   | Stable Input Clock;<br>Temperature<br>Gradient <10 °C/min;<br>800 Hz Loop BW            | _                | _                  | 45                     | ps/<br>°C/<br>min |

| Initial Frequency Accuracy in Digital Hold<br>Mode (first 100 ms with voltage and<br>temperature held constant)              | C <sub>DH_FA</sub>   | Stable Input Clock<br>Selected until entering<br>Digital Hold                           | _                | _                  | 5.5                    | ppm               |

| Clock Output Frequency Accuracy Over Temperature in Digital Hold Mode                                                        | C <sub>DH_T</sub>    | Constant Supply Voltage                                                                 | _                | 17.2               | 30                     | ppm<br>/°C        |

| Clock Output Frequency Accuracy Over<br>Supply Voltage in Digital Hold Mode                                                  | C <sub>DH_V33</sub>  | Constant Temperature                                                                    | _                | _                  | 600                    | ppm<br>/V         |

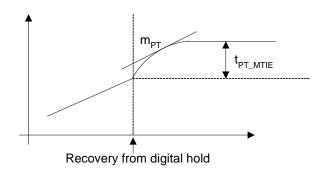

| Clock Output Phase Step <sup>3</sup> (See Figure 8)                                                                          | t <sub>PT_MTIE</sub> | When hitlessly recovering from Digital Hold mode                                        | -200             | 0                  | 200                    | ps                |

| Clock Output Phase Step Slope <sup>3</sup> (See Figure 8)                                                                    | m <sub>PT</sub>      | When hitlessly recovering from Digital Hold mode                                        |                  |                    |                        |                   |

| BWSEL[1:0] = 11, BWBOOST = 0<br>BWSEL[1:0] = 00, BWBOOST = 0<br>BWSEL[1:0] = 01, BWBOOST = 0<br>BWSEL[1:0] = 10, BWBOOST = 0 |                      | 6400 Hz, No Scaling<br>3200 Hz, No Scaling<br>1600 Hz, No Scaling<br>800 Hz, No Scaling | _<br>_<br>_<br>_ | <br> -<br> -<br> - | 10<br>5<br>2.5<br>1.25 | ps/<br>µs         |

#### Notes:

- 1. Higher PLL bandwidth settings provide smaller clock output wander with temperature gradient.

- 2. For reliable device operation, temperature gradients should be limited to 10 °C/min.

- **3.** Telcordia GR-1244-CORE requirements specify maximum phase transient slope during clock rearrangement in terms of nanoseconds per millisecond. The equivalent ps/μs unit is used here since the maximum phase transient magnitude for the Si5321 (tPT\_MTIE) never reaches one nanosecond.

**Table 5. Absolute Maximum Ratings**

| Parameter                                   | Symbol            | Value                             | Unit |

|---------------------------------------------|-------------------|-----------------------------------|------|

| 3.3 V DC Supply Voltage                     | V <sub>DD33</sub> | -0.5 to 3.6                       | V    |

| LVTTL Input Voltage                         | V <sub>DIG</sub>  | -0.3 to (V <sub>DD33</sub> + 0.3) | V    |

| Maximum Current any output PIN              |                   | ±50                               | mA   |

| Operating Junction Temperature              | T <sub>JCT</sub>  | -55 to 150                        | °C   |

| Storage Temperature Range                   | T <sub>STG</sub>  | -55 to 150                        | °C   |

| ESD HBM Tolerance (100 pf, 1.5 k $\Omega$ ) |                   | 1.0                               | kV   |

**Note:** Permanent device damage may occur if the Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Table 6. Thermal Characteristics**

| Parameter                              | Symbol | Test Condition | Value | Unit |

|----------------------------------------|--------|----------------|-------|------|

| Thermal Resistance Junction to Ambient | φја    | Still Air      | 34.7  | °C/W |

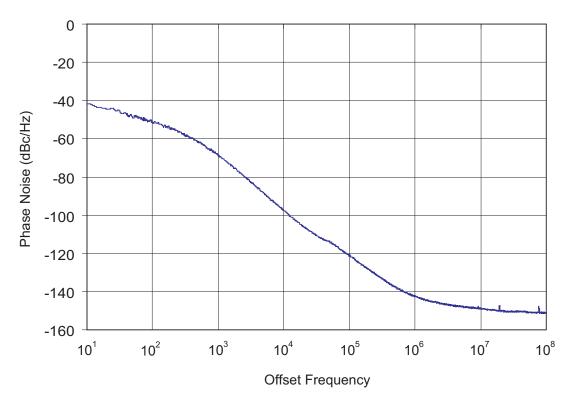

Figure 4. Typical Si5321 Phase Noise (CLKIN = 155.52 MHz, CLKOUT = 622.08 MHz, and Loop BW = 800 Hz)

Figure 5. Si5321 Typical Application Circuit (3.3 V Supply)

## 2. Functional Description

The Si5321 is a high-performance precision clock multiplication and clock generation device. This device accepts a clock input in the 19, 39, 78, 155, 311, or 622 MHz range, attenuates significant amounts of jitter, and multiplies the input clock frequency to generate a clock output in the 19, 39, 78, 155, 311, 622, 1250, or 2500 MHz range. Additional forward or reverse clock rate scaling by a factor of 255/238, 255/237, or 66/64 is provided. This allows systems to easily provide clocks that are scaled for forward error correction (FEC) rates. The 255/238 and 255/237 factors support the ITU-T G.709 requirements for optical transport unit (OTU) OC-48 and OC-192 rates. The 66/64 factor allows conversion between XSBI and 10 GbE Base R rates.

Typical applications for the Si5321 in SONET/SDH systems are generation and/or cleaning of 19.44, 38.88, 77.76, 155.52, 311.04, 622.08, 1244.16, or 2488.32 MHz clocks from 19.44, 38.88, 77.76, 155.52, 311.04, or 622.08 MHz clock sources.

The Si5321 employs Silicon Laboratories DSPLL® technology to provide excellent jitter performance while minimizing the external component count and maximizing flexibility and ease of use. The Si5321 DSPLL phase locks to the input clock signal, attenuates jitter, and multiplies the clock frequency to generate the device's SONET/SDH-compliant clock output. The DSPLL loop bandwidth is user selectable, allowing Si5321 jitter performance optimization for different applications. The Si5321 can produce a clock output with jitter generation as low as 0.3 ps<sub>RMS</sub> (see Table 4 on page 10), making the device an ideal solution for clock multiplication in SONET/SDH (including OC-48, OC-192, and OC768), Gigabit Ethernet, and 10 GbE systems.

The Si5321 monitors the clock input signal for loss-of-signal and provides a loss-of-signal (LOS) alarm when it detects missing pulses. The Si5321 provides a digital hold capability that allows the device to continue generation of a stable output clock when the input reference is lost.

## 2.1. DSPLL®

The Si5321's phase-locked loop (PLL) uses Silicon Laboratories' DSPLL technology to eliminate jitter, noise, and the need for external loop filter components found in traditional PLL implementations. This is achieved by using a digital signal processing (DSP) algorithm to replace the loop filter commonly found in analog PLL designs. This algorithm processes the phase detector error term and generates a digital control value to adjust the frequency of the voltage-

controlled oscillator (VCO). The technology produces low phase noise clocks with less jitter than is generated using traditional methods. See Figure 4 for an example phase noise plot. In addition, because external loop filter components are not required, sensitive noise entry points are eliminated thus making the DSPLL less susceptible to board-level noise sources. This digital technology also provides highly-stable and consistent operation over all process, temperature, and voltage variations. The benefits are smaller, lower power, cleaner, reliable, and easy-to-use clock circuits.

#### 2.1.1. Selectable Loop Filter Bandwidth

The digital characteristics of the DSPLL loop filter allow control of the loop filter parameters without the need to change external components. The Si5321 provides the user with up to eight user-selectable loop bandwidth settings for different system requirements. The base loop bandwidth is selected using the BWSEL[1:0] pins along with BWBOOST = 0 pins. When the BWBOOST is driven high, the bandwidth selected on the BWSEL[1:0] pins is doubled. (See Table 7.)

When the BWBOOST pin is asserted, the Si5321 shows improved jitter generation performance. The BWBOOST function is defined only when hitless recovery and FEC scaling are disabled. Therefore, when BWBOOST is high, the user must also drive FXDDELAY high and FEC[1:0] to 000 for proper operation.

### 2.2. Clock Input and Output Rate Selection

The Si5321 provides a 1/32x, 1/16x, 1/8x, 1/4x, 1/2x, 1x, 2x, 4x, 8x, 16x, 32x, 64x, or 128x clock frequency multiplication function with an option for additional frequency scaling by a factor of 255/238, 238/255, 255/237, 237/255, 66/64, or 64/66 for FEC rate compatibility. Output rates vary in accordance with the input clock rate. The multiplication factor is configured by selecting the input and output clock frequency ranges for the device.

The Si5321 accepts an input clock in the 19, 38, 77, 155, 311, or 622 MHz frequency range. The input frequency range is selected using the INFRQSEL[2:0] pins. The INFRQSEL[2:0] settings and associated output clock rates are listed in Table 8.

The Si5321's DSPLL phase locks to the clock input signal to generate an internal VCO frequency that is a multiple of the input clock frequency. The internal VCO frequency is divided down to produce a clock output in the 19, 39, 78, 155, 311, 622, 1250, or 2500 MHz frequency range. The clock output range is selected using the frequency select (FRQSEL[2:0]) pins. The FRQSEL[2:0] settings and associated output clock rates are given in Table 9.

The Si5321 clock input frequencies are variable within the range specified in Table 3 on page 7. The output rates are scaled accordingly. If a 19.44 MHz input clock is used, the clock output frequency is 19.44, 38.88, 77.76, 155.52 MHz, etc.

Table 7. Loop Bandwidth and FEC Settings

| Exter   | nal Input | S     | Effective          | Effective         |

|---------|-----------|-------|--------------------|-------------------|

|         | BWSEL     | FEC   | FEC                | PLL               |

| BWBOOST | [1:0]     | [2:0] | Conversion<br>Rate | Bandwidth<br>(Hz) |

| 0       | 00        | 000   | 1/1                | 3200              |

| 0       | 00        | 000   | 255/238            | 3200              |

| 0       | 00        | 010   | 238/255            |                   |

| 0       | 00        | 010   |                    | 3200              |

| 0       | 00        | 100   | Reserved 255/237   | 3200              |

| 0       | 00        | 101   | 237/255            | 3200              |

| 0       | 00        | 110   | 66/64              | 3200              |

| 0       | 00        | 111   | 64/66              | 3200              |

|         |           |       |                    |                   |

| 0       | 10        | 000   | 1/1                | 800               |

| 0       | 10        | 001   | 255/238            | 800               |

| 0       | 10        | 010   | 238/255            | 800               |

| 0       | 10        | 011   | Reserved           |                   |

| 0       | 10        | 100   | 255/237            | 800               |

| 0       | 10        | 101   | 237/255            | 800               |

| 0       | 10        | 110   | 66/64              | 800               |

| 0       | 10        | 111   | 64/66              | 800               |

| 0       | 11        | 000   | 1/1                | 6400              |

| 0       | 11        | 001   | 255/238            | 6400              |

| 0       | 11        | 010   | 238/255            | 6400              |

| 0       | 11        | 011   | Reserved           | _                 |

| 0       | 11        | 100   | 255/237            | 6400              |

| 0       | 11        | 101   | 237/255            | 6400              |

| 0       | 11        | 110   | 66/64              | 6400              |

| 0       | 11        | 111   | 64/66              | 6400              |

| 1       | 00        | 0xx   | 1/1                | 6400              |

| 1       | 10        | 0xx   | 1/1                | 1600              |

| 1       | 11        | 0xx   | 1/1                | 12800             |

| 1       | 01        | 0xx   | 1/1                | 3200              |

| 0       | 01        | 000   | 1/1                | 1600              |

| 0       | 01        | 001   | 255/238            | 1600              |

| 0       | 01        | 010   | 238/255            | 1600              |

| 0       | 01        | 011   | Reserved           | _                 |

| 0       | 01        | 100   | 255/237            | 1600              |

| 0       | 01        | 101   | 237/255            | 1600              |

| 0       | 01        | 110   | 66/64              | 1600              |

| 0       | 01        | 111   | 64/66              | 1600              |

**Table 8. Nominal Clock Input Frequencies**

| Input Clock<br>Frequency<br>Range | INFRQSEL2 | INFRQSEL1 | INFRQSEL0 |

|-----------------------------------|-----------|-----------|-----------|

| Reserved                          | 1         | 1         | 1         |

| 622 MHz                           | 1         | 1         | 0         |

| 311 MHz                           | 1         | 0         | 1         |

| 155 MHz                           | 1         | 0         | 0         |

| 77 MHz                            | 0         | 1         | 1         |

| 38 MHz                            | 0         | 1         | 0         |

| 19 MHz                            | 0         | 0         | 1         |

| Reserved                          | 0         | 0         | 0         |

**Table 9. Nominal Clock Output Frequencies**

| Output Clock<br>Frequency<br>Range | FRQSEL2 | FRQSEL1 | FRQSEL0 |

|------------------------------------|---------|---------|---------|

| 2,488.32 MHz                       | 1       | 1       | 1       |

| 1244.16 MHz                        | 1       | 1       | 0       |

| 622.08 MHz                         | 0       | 1       | 1       |

| 311.04 MHz                         | 1       | 0       | 1       |

| 155.52 MHz                         | 0       | 1       | 0       |

| 77.76 MHz                          | 1       | 0       | 0       |

| 38.88 MHz                          | 0       | 0       | 0       |

| 19.44 MHz                          | 0       | 0       | 1       |

#### 2.2.1. FEC Rate Conversion

The Si5321 provides a 1/32x, 1/16x, 1/8x, 1/4x, 1/2x, 1x, 2x, 4x, 8x, 16x, 32x, 64x, or 128x clock frequency multiplication function with an option for additional forward or reverse frequency scaling by a factor of 255/238 (15/14), 255/237 (85/79), or 66/64 (33/32) for FEC rate conversion applications. The 255/237 and the 66/64 rate conversions requires the input clock rate to be in the 155 MHz or higher ranges. The multiplication factor is configured by selecting the input and output clock frequency ranges for the device. The additional frequency scaling for FEC rate conversion is selected using the FEC[2:0] control inputs.

For example, a 622.08 MHz output clock (a non-FEC rate) can be generated from a 19.44 MHz input clock (a non-FEC rate) by setting INFRQSEL[2:0] = 001 (19.44 MHz range), setting FRQSEL[2:0] = 011 (32x multiplication) and setting FEC[2:0] = 000 (no FEC scaling). A 666.51 MHz output clock (an FEC rate) can be generated from a 19.44 MHz input clock (a non-FEC rate) by setting INFRQSEL[2:0] = 001 (19.44 MHz range), setting FRQSEL[2:0] = 011 (32x multiplication)

and setting FEC[2:0] = 001 (255/238 FEC scaling).

Finally, a 622.08 MHz output clock (a non-FEC rate) can be generated from a 20.83 MHz input clock (an FEC rate) by setting INFRQSEL[2:0] = 001 (19.44 MHz range), setting FRQSEL[2:0] = 011 (32x multiplication) and setting FEC[2:0] = 010 (238/255 FEC scaling).

#### 2.3. PLL Performance

The Si5321 PLL provides extremely low jitter generation, high jitter tolerance, and a well-controlled jitter transfer function with low peaking and a high degree of jitter attenuation.

#### 2.3.1. Jitter Generation

Jitter generation is defined as the amount of jitter produced at the output of the device with a jitter free input clock. Generated jitter arises from sources within the VCO and other PLL components. Jitter generation is a function of the PLL bandwidth setting. Higher loop bandwidth settings may result in lower jitter generation but may also result in less attenuation of jitter than might be present on the input clock signal.

#### 2.3.2. Jitter Transfer

Jitter transfer is defined as the ratio of output signal jitter to input signal jitter for a specified jitter frequency. The jitter transfer characteristic determines the amount of input clock jitter that passes to the outputs. The DSPLL technology used in the Si5321 provides tightly-controlled jitter transfer curves because the PLL gain parameters are determined by digital circuits that do not vary over supply voltage, process, and temperature. In a system application, a well-controlled transfer curve minimizes the output clock jitter variation from board to board and provides more consistent system level jitter performance.

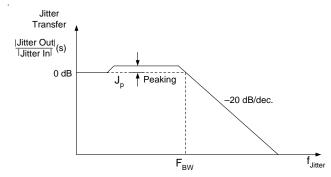

The jitter transfer characteristic is a function of the BWSEL[1:0] setting. Lower bandwidth settings result in more jitter attenuation of the incoming clock but may result in higher jitter generation. Table 4 on page 10 gives the 3 dB bandwidth and peaking values for specified BWSEL settings. Figure 6 shows the jitter transfer curve mask.

Figure 6. PLL Jitter Transfer Mask/Template

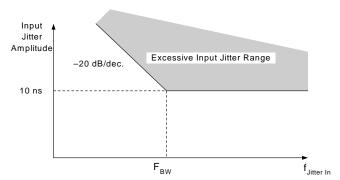

#### 2.3.3. Jitter Tolerance

Jitter tolerance for the Si5321 is defined as the maximum peak-to-peak sinusoidal jitter that can be present on the incoming clock. The tolerance is a function of the jitter frequency because tolerance improves for lower input jitter frequency.

Figure 7. Jitter Tolerance Mask/Template

#### 2.4. Loss-of-Signal Alarm

The Si5321 has loss-of-signal (LOS) circuitry that constantly monitors the CLKIN input clock for missing pulses. The LOS circuitry sets a LOS output alarm signal when missing pulses are detected.

The LOS circuitry operates as follows. Regardless of the selected input clock frequency range, the LOS circuitry divides down the input clock into the 19 MHz range. The LOS circuitry then over-samples this divided down input clock to search for extended periods of time without input clock transitions. If the LOS circuitry detects four consecutive samples of the divided down input clock that are the same state (i.e., 1111 or 0000), a LOS condition is declared; the Si5321 goes into digital hold mode, and the LOS output alarm signal is set high. The LOS sampling circuitry runs at a frequency of f<sub>O 78</sub>, where f<sub>O 78</sub> is the output clock frequency when the FRQSEL[2:0] pins are set to 100. Figure 3 on page 5 and Table 3 on page 7 list the minimum and maximum transitionless time periods required for declaring a LOS on the input clock (t<sub>I OS</sub>).

Once the LOS alarm is asserted, it is held high until the input clock is validated over a time period designated by the VALTIME pin. When VALTIME is low, the validation time period is about 1 ms. When VALTIME is high, the validation time period is about 100 ms. If another LOS condition is detected on the input clock during the validation time (i.e., if another set of 1111 or 0000 samples are detected), the LOS alarm remains asserted and the validation time starts over. When the LOS alarm is finally released, the Si5321 exits digital hold mode and locks to the input clock. The LOS alarm is automatically set high at power-on and at every low-to-high transition of the RSTN/CAL pin. In these cases, the Si5321 undergoes a self-calibration before releasing the LOS alarm and locking to the input clock.

The Si5321 also provides an output indicating the digital hold status of the device, DH\_ACTV. The Si5321 only enters the digital hold mode upon the loss of the input clock. When this occurs, the LOS alarm will also be active. Therefore, applications that require monitoring of the status of the Si5321 need only monitor the CAL\_ACTV and either the LOS or DH\_ACTV outputs to know the state of the device.

#### 2.5. Digital Hold of the PLL

When no valid input clock is available, the Si5321 digitally holds the internal oscillator to its last frequency value. This provides a stable clock to the system until an input clock is valid again. This clock maintains stable operation in the presence of constant voltage and temperature. The frequency accuracy specifications for digital hold mode are given in Table 4 on page 10.

#### 2.6. Hitless Recovery from Digital Hold

When the Si5321 device is locked to a valid input clock, a loss of the input clock switches the device to digital hold mode. When the input clock signal returns, the device performs a hitless transition from digital hold mode back to the selected input clock. That is, the device executes "phase build-out" to absorb the phase difference between the internal VCO clock operating in digital hold mode and the new/returned input clock. The maximum phase step seen at the clock output during this transition, and the maximum slope of this step, is specified in Table 4 on page 10.

Asserting the Fixed Delay (FXDDELAY) pin disables this feature and the output clock phase and frequency locks with a known phase relationship to the input clock. Consequently, abrupt phase change on the input clock propagates through the device and the output slews at the loop bandwidth until the phase relationship is restored.

Figure 8. Recovery from Digital Hold

#### 2.7. Reset

The Si5321 provides a Reset/Calibration pin (RSTN/CAL) that resets the device and disables all of the device outputs. When the RSTN/CAL pin is driven low, the internal circuitry enters reset mode and all LVTTL outputs are forced into a high-impedance state. Also, the CLKOUT+ and CLKOUT– pins are connected to  $V_{DD25}$  through  $100\ \Omega$  on-chip resistors. This feature is useful for applications that employ redundant clock sources and for in-circuit test applications. A low-to-high transition on RSTN/CAL initializes all digital logic to a known condition and initiates self-calibration of the DSPLL. At the completion of self-calibration, the DSPLL begins to lock to the clock input signal.

#### 2.8. PLL Self-Calibration

The Si5321 achieves optimal jitter performance by using self-calibration circuitry to set the VCO center frequency and loop gain parameters within the DSPLL. Internal circuitry generates self calibration automatically on powerup or after a loss-of-power condition. Self-calibration also can be manually initiated by a low-to-high transition on the RSTN/CAL input.

A self-calibration should be initiated after changing the state of the FEC[2:0] inputs. Whether manually initiated or automatically initiated at powerup, the self-calibration process requires the presence of a valid input clock.

If the self-calibration is initiated without a valid input clock, the device waits for a valid input clock before executing the self-calibration. The Si5321 does not provide an output clock while waiting for a valid input clock or while executing its self-calibration. When the input clock is validated, the calibration procedure executes to completion; the device locks to the input clock, and the output clock turns on. Subsequent losses of the input clock do not require self-calibration. If the input clock is lost following self-calibration, the device enters digital hold mode with the output clock frequency held to its last value before the LOS condition was

detected. When the input clock returns and is validated, the device exits digital hold mode by re-locking to the input clock without executing another self-calibration.

#### 2.9. Bias Generation Circuitry

The Si5321 makes use of an external resistor to set internal bias currents. The external resistor allows precise generation of bias currents, which significantly reduces power consumption and variation as compared with traditional implementations that use an internal resistor. The bias generation circuitry requires a 10 k $\Omega$  (1%) resistor connected between REXT and GND.

#### 2.10. Differential Input Circuitry

The Si5321 provides a differential input for the clock input, CLKIN. This input is internally-biased to a voltage of  $V_{\rm ICM}$  (see Table 2 on page 6) and may be driven by a differential or single-ended driver circuit. For transmission line termination, the termination resistor is connected externally as shown.

#### 2.11. Differential Output Circuitry

The Si5321 utilizes a current mode logic (CML) architecture to drive the differential clock output, CLKOUT.

For single-ended output operation simply connect to either CLKOUT+ or CLKOUT- and leave the unused signal unconnected.

#### 2.12. Power Supply Connections

The Si5321 incorporates an on-chip voltage regulator to power the device from a 3.3 V supply. The voltage regulator requires an external compensation circuit of one resistor and one capacitor to ensure stability over all operating conditions.

Internally, the Si5321  $V_{DD33}$  pins are connected to the on-chip voltage regulator input and to the device's LVTTL I/O circuitry. The  $V_{DD25}$  pins supply power to the core DSPLL circuitry, and are also used for connection of the external compensation circuit.

The regulator's compensation circuit is a resistor and a capacitor in series between the  $V_{DD25}$  node and ground. Typically, the resistor is incorporated into the capacitor's equivalent series resistance (ESR). The target RC time constant for this combination is 15 to 50  $\mu s$ . The capacitor used in the Si5321 evaluation board is a 33  $\mu f$  tantalum capacitor with an ESR of 0.8  $\Omega$ . This gives an RC time constant of 26.4  $\mu s$ . The Venkel part number TA6R3TCR336KBR is an example of a capacitor that meets these specifications. (See Figure 5.)

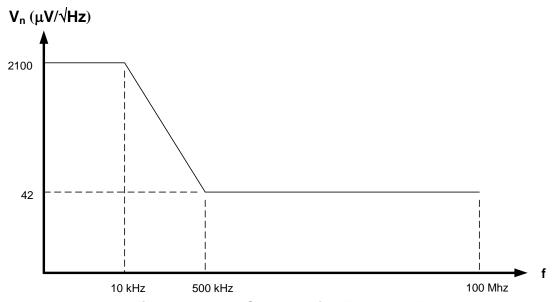

To get optimal performance from the Si5321 device, the power supply noise spectrum must comply with the plot in Figure 9. This plot shows the power supply noise tolerance mask for the Si5321. The customer should provide a 3.3 V supply that does not have noise density in excess of the amount shown in the diagram. However, the diagram cannot be used as spur criteria for a power supply that contains single tone noise.

Figure 9. Power Supply Noise Tolerance Mask

## 2.13. Design and Layout Guidelines

Precision clock circuits are susceptible to board noise and EMI. To take precautions against unacceptable levels of board noise and EMI affecting performance of the Si5321, consider the following:

- Power the device from 3.3 V since the internal regulator provides >40 dB of isolation to the V<sub>DD25</sub> pins (which power the PLL circuitry).

- When powering the device from 3.3 V, use an isolated, local plane to connect the V<sub>DD25</sub> pins.

Avoid running signal traces over or below this plane without a ground plane in between.

- Route all I/O traces between ground planes as much as possible

- Maintain an input clock amplitude in the 200 mV<sub>PP</sub> to 500 mV<sub>PP</sub> differential range.

- Excessive high-frequency harmonics of the input clock should be minimized. The use of filters on the input clock signal can be used to remove highfrequency harmonics.

## 3. Pin Descriptions: Si5321

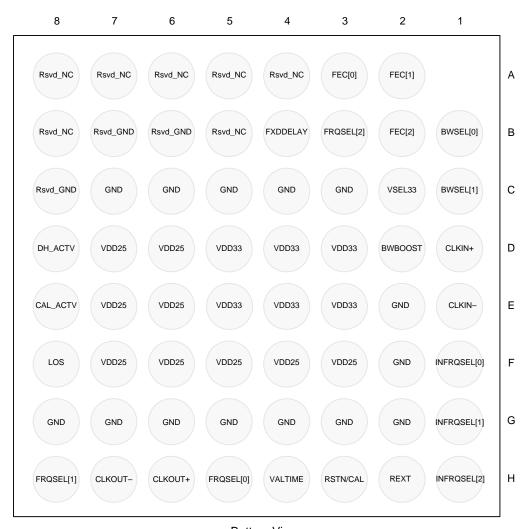

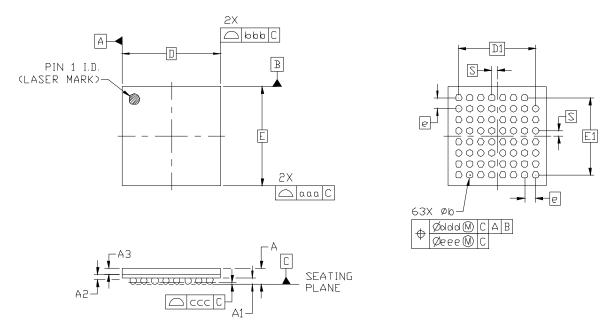

**Bottom View**

Figure 10. Si5321 Pin Configuration (Bottom View)

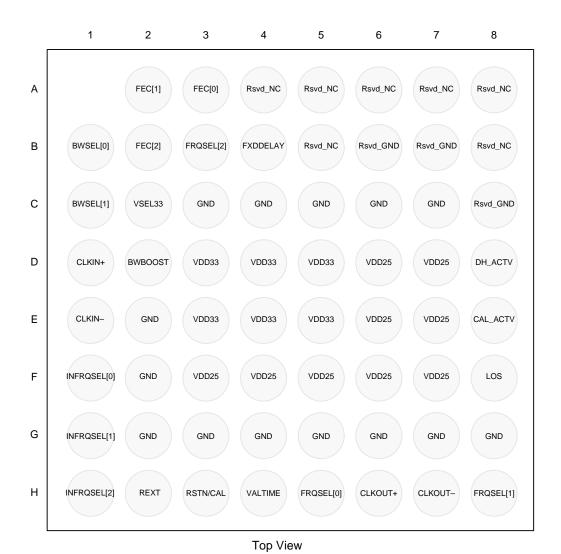

Figure 11. Si5321 Pin Configuration (Transparent Top View)

**Table 10. Si5321 Pin Descriptions**

| Pin #          | Pin Name                                  | I/O | Signal Level                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|-------------------------------------------|-----|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|