# [MG2420] Datasheet

(No. ADS0701)

V1.2

The reproduction of this datasheet is NOT allowed without approval of RadioPulse Inc. All information and data contained in this datasheet are subject to change without notice. This publication supersedes and replaces all information previously supplied. RadioPulse Inc. has no responsibility to the consequence of using the patents describes in this document.

## **REVISION HISTORY**

| Version | Date       | Description                                                                                                                                                                                                                                                                 |

|---------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V1.0    | 2013.10.24 | First version release.                                                                                                                                                                                                                                                      |

| V1.1    | 2014.04.21 | <ul> <li>Sec 4.1</li> <li>Temperature updated.</li> <li>Sec 5</li> <li>Application circuit is updated.</li> </ul>                                                                                                                                                           |

| V1.2    | 2014.09.01 | <ul> <li>Sec 4.8</li> <li>Crystal Oscillator parameters (TYP and MAX value for ESR, C<sub>0</sub> and C<sub>L</sub>) are updated.</li> <li>Sec 5</li> <li>Table 3. Bill of Materials is updated. C<sub>11</sub> and C<sub>12</sub> is changed from 30pF to 13pF.</li> </ul> |

## CONTENTS

| 1.  | INTRODUCTION                                   |    |

|-----|------------------------------------------------|----|

| 1.1 | .1. APPLICATIONS                               | 8  |

| 2.  | KEY FEATURES                                   | 9  |

| 2.2 | .1. RF TRANSCEIVER                             | 9  |

| 2.2 | .2. INTEGRATED MAC                             | 9  |

| 2.3 | .3. Clock Inputs                               | 9  |

| 2.4 | .4. Power                                      |    |

| 2.  | .5. Package                                    |    |

| 3.  | PIN DESCRIPTION                                |    |

| 4.  | ELECTRICAL CHARACTERISTICS                     | 14 |

| 4.1 | .1. Absolute Maximum Ratings                   |    |

| 4.2 | .2. Recommended Operating Conditions           |    |

| 4.3 | .3. DIGITAL I/O DC CHARACTERISTICS             |    |

| 4.4 | .4. CURRENT CONSUMPTION                        |    |

| 4.  | .5. RF Receive Section                         |    |

|     | 4.5.1. Chip Rate of 2Mcps (RF Bandwidth: 2MHz) |    |

|     | 4.5.2. Chip Rate of 4Mcps (RF Bandwidth: 4MHz) |    |

| 4.0 | .6. RF TRANSMIT SECTION                        |    |

|     | 4.6.1. Chip Rate of 2Mcps (RF Bandwidth: 2MHz) |    |

|     | 4.6.2. Chip Rate of 4Mcps (RF Bandwidth: 4MHz) |    |

| 4.  | .7. FREQUENCY SYNTHESIZER CHARACTERISTICS      |    |

| 4.8 | .8. Crystal Oscillator                         |    |

| 4.9 | .9. Analog Temperature Sensor                  |    |

| 5.  | APPLICATION                                    |    |

| 6.  | FUNCTIONAL DESCRIPTION                         |    |

| 6.2 | .1. Block Diagram                              |    |

| 6.2 | .2. Data Rate                                  | 25 |

| 6.3 | .3. Forward Error Correction(FEC)              |    |

| 6.4 | .4. Packet Format                              |    |

| 6.  | .5. RSSI and Energy Detection                  |    |

| 6.0 | .6. Clear Channel Assessment (CCA)             |    |

| 6.  | .7. Link Quality Indicator (LQI)               |    |

| 6.8 | .8. Integrated MAC                             |    |

| 6.8.1.   | RX Mode                                       |  |

|----------|-----------------------------------------------|--|

| 6.8.2.   | TX Mode                                       |  |

| 6.8.3.   | Data Encryption                               |  |

| 6.9. F   | REQUENCY SYNTHESIZER(PLL)                     |  |

| 6.10.    | Crystal Oscillator (XOSC)                     |  |

| 6.11.    | Voltage Regulator                             |  |

| 6.12.    | Temperature Sensor                            |  |

| 6.13.    | CLOCK CONTROL                                 |  |

| 7. MICR  | OCONTROLLER INTERFACE                         |  |

| 7.1. S   | PI PROTOCOL                                   |  |

| 7.1.1.   | SPI Timing Description                        |  |

| 7.1.2.   | Register Access                               |  |

| 7.1.3.   | FIFO Access                                   |  |

| 7.2. F   | RESETB AND DVREGEN                            |  |

| 7.3. I   | NTERRUPT                                      |  |

| 7.3.1.   | Signaling                                     |  |

| 7.3.2.   | Interrupt Source & Masking                    |  |

| 7.4. (   | DTHER DIGITAL INTERFACE                       |  |

| 7.5. E   | XTERNAL CLOCK OUTPUT                          |  |

| 8. OPER  | ATING DESCRIPTION                             |  |

| 8.1. E   | Basic Operating Mode                          |  |

| 9. REGIS | STER MAP                                      |  |

| 9.1. N   | лодем Registers                               |  |

| 9.2.     | Clock Registers                               |  |

| 9.3. E   | Digital Interface Pin Registers               |  |

| 9.4. F   | LL REGISTERS                                  |  |

| 9.5. F   | RF Registers                                  |  |

| 9.6. N   | Aiscellaneous Registers                       |  |

| 9.7. S   | Status and Monitoring Registers               |  |

| 9.8. N   | AAC REGISTERS                                 |  |

| 9.8.1.   | MAC/Security Address FIFO Map                 |  |

| 9.8.2.   | Common Control Register Description           |  |

| 9.8.3.   | RX FIFO control Register Description          |  |

| 9.8.4.   | TX FIFO Control Register Description          |  |

| 9.8.5.   | RX Security FIFO Control Register Description |  |

| 9.8.6.   | TX Security FIFO Control Register Description |  |

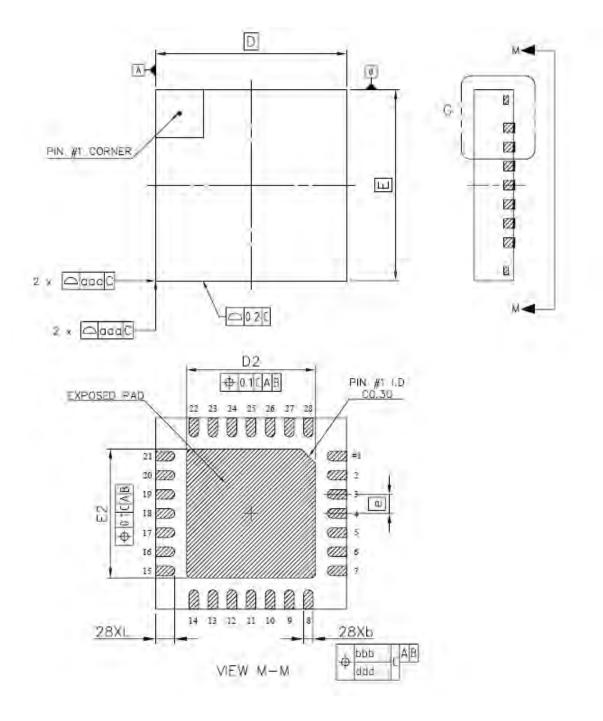

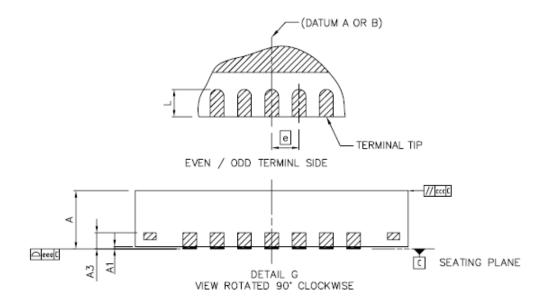

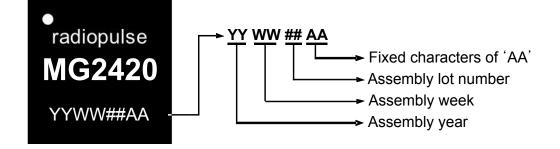

| 10.  | PAC | CKAGE INFORMATION | 77 |

|------|-----|-------------------|----|

| 10.1 | L.  | DIMENSIONS        | 77 |

| 10.2 | 2.  | Marking           | 78 |

| 11.  | ABE | BREVIATIONS       | 79 |

| 12.  | REF | ERENCES           | 80 |

## FIGURES

| FIGURE 1. MG2420 PIN-OUT DIAGRAM                                              | 11   |

|-------------------------------------------------------------------------------|------|

| FIGURE 2. MG2420 APPLICATION CIRCUIT                                          |      |

| FIGURE 3. MG2420 BLOCK DIAGRAM                                                |      |

| FIGURE 4. BASEBAND PHY BLOCK DIAGRAM                                          | 24   |

| FIGURE 5. MODULATED SIGNAL SPECTRUM FOR 2MCPS MODE                            | 26   |

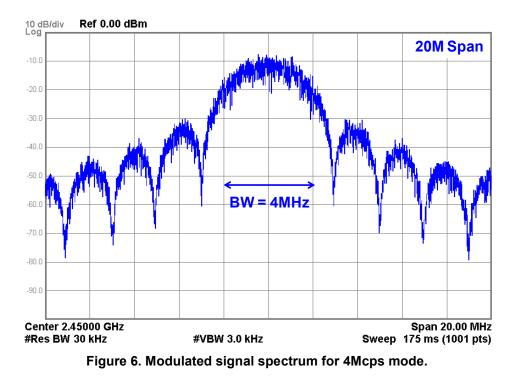

| FIGURE 6. MODULATED SIGNAL SPECTRUM FOR 4MCPS MODE                            | 27   |

| FIGURE 7. CONVOLUTIONAL ENCODER WITH RATE OF 1/2.                             | 27   |

| FIGURE 8. PACKET FORMAT                                                       | 28   |

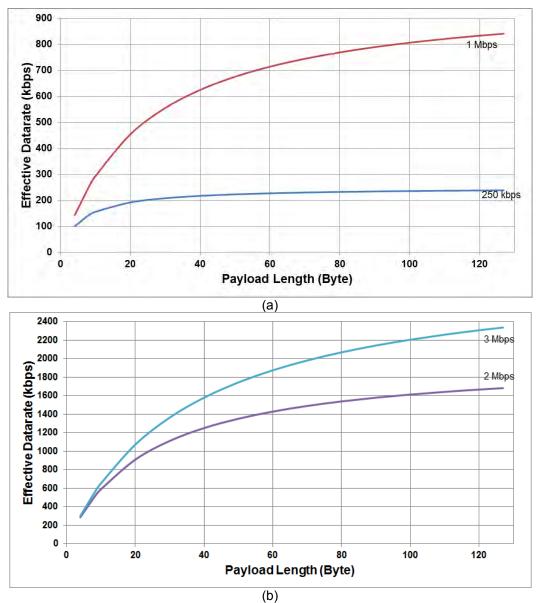

| FIGURE 9. EFFECTIVE PAYLOAD DATA RATE. (A) 2MCPS MODE. (B) 4MCPS MODE.        | 29   |

| FIGURE 10. TYPICAL RSSI VALUE VS. RX INPUT POWER FOR 250KBPS                  |      |

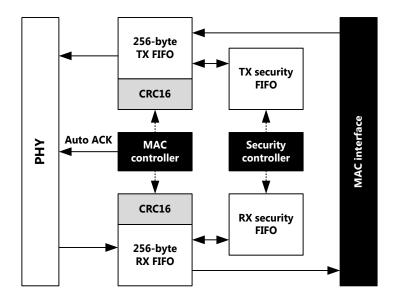

| FIGURE 11. INTEGRATED MAC STRUCTURE                                           | 33   |

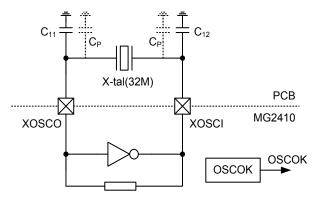

| FIGURE 12. SIMPLIFIED CRYSTAL OSCILLATOR SCHEMATIC.                           | 42   |

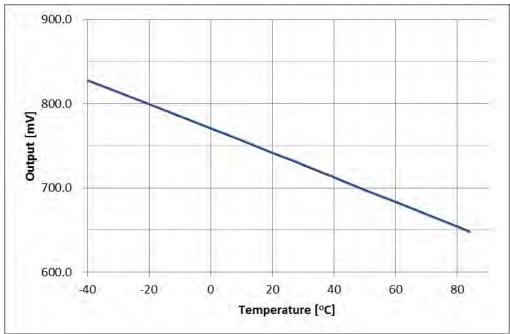

| FIGURE 13. TEMPERATURE SENSOR OUTPUT VOLTAGE                                  | 43   |

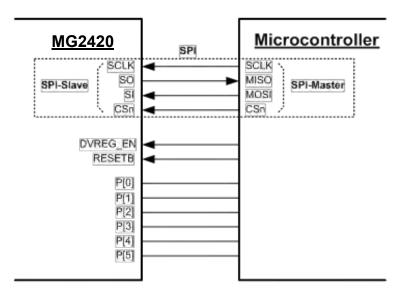

| FIGURE 14. MICROCONTROLLER TO MG2420 INTERFACES.                              |      |

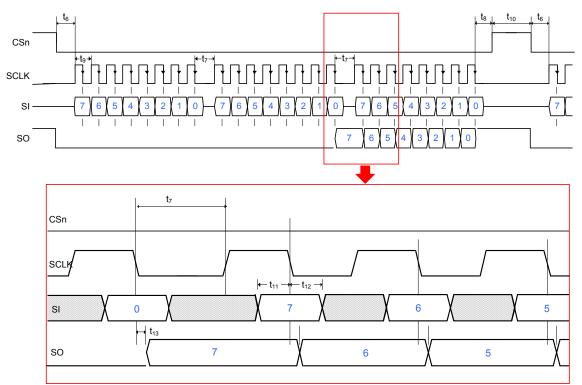

| FIGURE 15. SPI TIMING DIAGRAM                                                 | 46   |

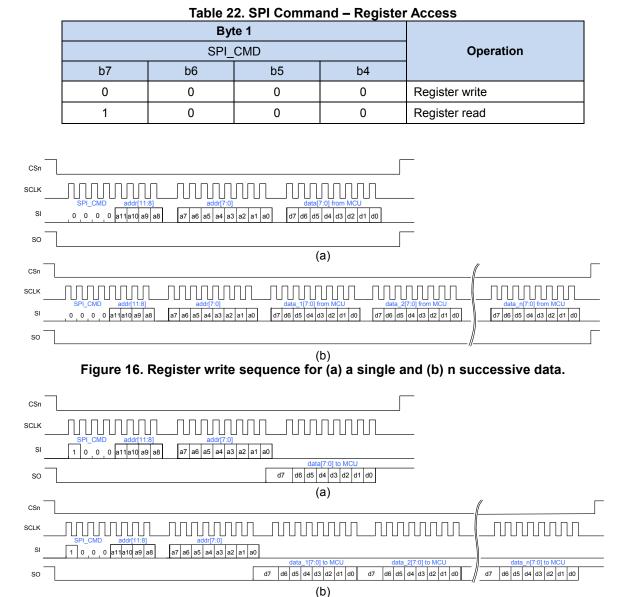

| FIGURE 16. REGISTER WRITE SEQUENCE FOR (A) A SINGLE AND (B) N SUCCESSIVE DATA | . 47 |

| FIGURE 17. REGISTER READ SEQUENCE FOR (A) A SINGLE AND (B) N SUCCESSIVE DATA  | 47   |

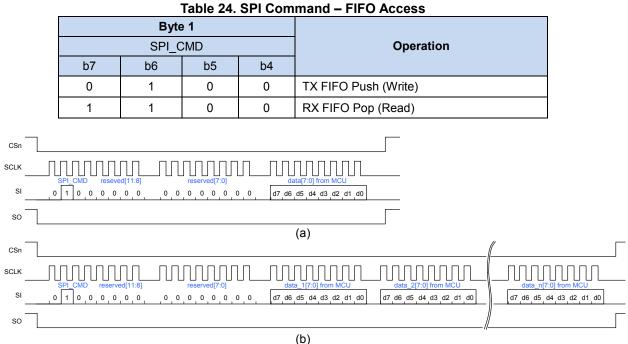

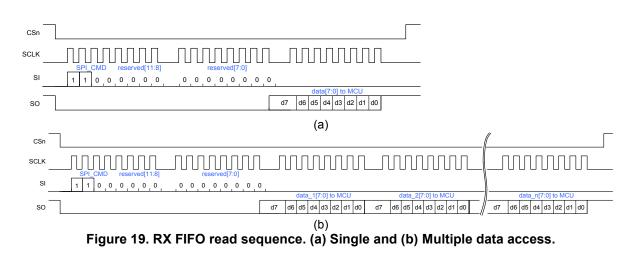

| FIGURE 18. TX FIFO WRITE SEQUENCE. (A) SINGLE AND (B) MULTIPLE DATA ACCESS    | 48   |

| FIGURE 19. RX FIFO READ SEQUENCE. (A) SINGLE AND (B) MULTIPLE DATA ACCESS     | 48   |

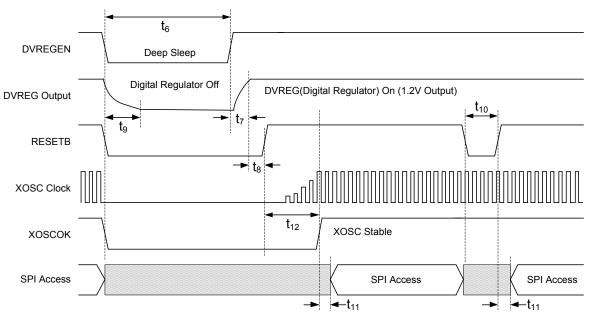

| FIGURE 20. RESETB AND DVREGEN SIGNAL DIAGRAM                                  | 49   |

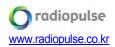

| FIGURE 21. GPIO PAD BLOCK DIAGRAM                                             | 52   |

| FIGURE 22. BASIC MG2420 STATE TRANSITION DIAGRAM                              |      |

| FIGURE 23. OVERALL REGISTER ADDRESS SPACE                                     | 57   |

## TABLES

| TABLE 1. MG2420 PIN DESCRIPTION                     | 11 |

|-----------------------------------------------------|----|

| TABLE 2. I/O EQUIVALENT CIRCUIT SUMMARY             | 13 |

| TABLE 3. BILL OF MATERIALS FOR FIGURE 2             | 22 |

| TABLE 4. DATA RATE MODES FOR 2MCPS                  |    |

| TABLE 5. DATA RATE MODES FOR 4MCPS                  |    |

| TABLE 6. PUNCTURING PATTERN                         |    |

| TABLE 7. RSSI MEASUREMENT                           | 30 |

| TABLE 8. RSSI CHARACTERISTICS                       | 30 |

| TABLE 9. CCA CONFIGURATION                          |    |

| TABLE 10. LQI CONFIGURATION                         | 32 |

| TABLE 11. MAC/SECURITY FIFO ADDRESS MAP             |    |

| TABLE 12. MAC/SECURITY CONTROL REGISTERS            |    |

| TABLE 13. RX FIFO CONTROL REGISTERS                 |    |

| TABLE 14. TX FIFO CONTROL REGISTERS                 | 37 |

| TABLE 15. TX SECURITY FIFO CONTROL REGISTERS        | 39 |

| TABLE 16. RX SECURITY FIFO CONTROL REGISTERS        |    |

| TABLE 17. CENTER FREQUENCY ASSIGNMENT               | 41 |

| TABLE 18. TEMPERATURE SENSOR CHARACTERISTICS        | 43 |

| TABLE 19. OPERATING CLOCK SETTING                   | 44 |

| TABLE 20. SPI TIMING CHARACTERISTICS                | 46 |

| TABLE 21. SPI FORMAT – REGISTER ACCESS              | 46 |

| TABLE 22. SPI COMMAND – REGISTER ACCESS             | 47 |

| TABLE 23. SPI FORMAT – FIFO ACCESS                  |    |

| TABLE 24. SPI COMMAND – FIFO ACCESS                 | 48 |

| TABLE 25. RESETB AND DVREGEN TIMING CHARACTERISTICS | 49 |

| TABLE 26. INTERRUPT SUMMARY                         | 50 |

| TABLE 27. GPIO DRIVING STRENGTH                     | 51 |

| TABLE 28. GPIO CONFIGURATION TABLE FOR PS AND SPU   |    |

| TABLE 29. GPIO RESET STATE                          | 52 |

| TABLE 30. EXTERNAL CLOCK CONFIGURATION              | 53 |

## 1. INTRODUCTION

MG2420 is a low-power 2.4GHz IEEE 802.15.4 and ZigBee compliant radio transceiver. Operation frequency of MG2420 covers an ISM band of 2.4~2.48GHz. In addition to the standard data-rate specified in IEEE802.15.4, MG2420 provides enhanced multiple data rates with channel coding (1M~3Mbps).

MG2420 can be controlled by an external microcontroller, and its operations can be configured through a high speed Serial Peripheral Interface (SPI).

#### Ultra Low Power Consumption:

The current consumption of MG2420 is very low; which is 15.4 mA in Rx mode and 16.1 mA in Tx mode with output Power of 0 dBm. Utilization of higher data rate (~3Mbps) helps minimizing the time for transmission and reception, which leads to further reduction of power consumption.

#### Low Cost Solution:

MG2420 is a single chip RF transceiver, which includes RF front-end, VCO, PLL, and digital block including baseband modem, MAC, power management, and a high-speed SPI. It's packaged in compact 4x4mm package. Only small numbers of external components - RF matching network, crystal, bias resistor and antenna - are required as application circuit; this leads to the low cost solution.

#### Improved Interference Rejection and Longer Range:

MG2420 shows excellent interference rejection performance; it can receive wanted signal with the presence of interference from ZigBee or other communication devices (i.e. Wi-Fi or Bluetooth). It has a longer communication range based on high transmit power up to +9 dBm and high sensitivity of -97dBm at 250Kbps mode.

#### **1.1. APPLICATIONS**

- Home Automation and Security

- Automatic Meter Reading

- Factory Automation and Motor Control

- Energy Management

- Remote Keyless Entry with Acknowledgement

- Low Power Telemetry

- Health-care equipment

- PC peripherals

- Toys and Gaming peripherals

- Remote Controller for Consumer Electronics

- Audio and Video Applications

## 2. KEY FEATURES

#### 2.1. RF Transceiver

- Single-chip 2.4GHz RF Transceiver

- Low-power consumption

- 15.4mA at RX mode

- 16.1mA at TX mode with 0 dBm output

- 28.4mA at TX mode with +9 dBm output

- High RX Sensitivity

- -97dBm @ 250kbps (2Mcps Mode)

- -93dBm @ 1Mbps (2Mcps Mode)

- -90dBm @ 2Mbps (4Mcps Mode)

- -86dBm @ 3Mbps (4Mcps Mode)

- No External T/R Switch and Filter needed

- On-chip VCO, LNA, and PA

- Programmable Output Power up to +9 dBm

- Excellent TX EVM: 6% for 2Mcps mode, 8% for 4Mcps mode

- Direct Sequence Spread Spectrum

- MSK(O-QPSK) Modulation

- Channel coding with various rates of 1/2, 3/4

- Scalable Data Rate

- 250kbps for IEEE 802.15.4 and ZigBee applications

- 1Mbps for applications beyond IEEE 802.15.4 with RF bandwidth of 2MHz

- 2~3Mbps for applications beyond IEEE 802.15.4 with RF bandwidth of 4MHz

- Digital RSSI Output

- Compliant to IEEE802.15.4

## 2.2. Integrated MAC

- Two 256-byte FIFOs

- FIFO management

- AES-128 Engine

- CRC-16 Computation and Check

- Automatic ACK transmission

## 2.3. Clock Inputs

■ 32MHz Crystal for System Clock

### 2.4. Power

- 1.2V(Core)/1.8~3.6V(I/O) Operation

- Several On-chip Voltage Regulator for Analog part and Digital part separately.

- Power Supply Range for Internal Regulator(1.8V(Min) ~ 3.6V(Max))

- Power Management Scheme with Deep Sleep Mode Support; Current consumption under 1µA

## 2.5. Package

■ Lead-Free/RoHS 28-pin QFN Package (4mm x4mm x 0.85mm)

## 3. PIN DESCRIPTION

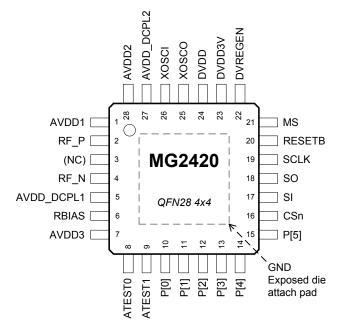

MG2420 pin-out diagram and description are shown in [Figure 1] and [Table 1], respectively.

#### Figure 1. MG2420 Pin-out Diagram

**Note:** The exposed die pad is located at the bottom of a chip and electrically connected to the die ground inside the package. It shall be soldered to ground on the board.

| Radio, Sy | Radio, Synthesizer, and Oscillator |            |                                                                                                                                                                  |  |  |  |

|-----------|------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin       | Pin Name                           | Pin type   | Pin Description                                                                                                                                                  |  |  |  |

| 2         | RF_P                               | RF I/O     | Positive RF input signal to LNA in RX mode.<br>Positive RF output signal from PA in TX mode.<br>It should be biased by AVDD_DCPL1. Refer to Figure 2<br>(Sec.5). |  |  |  |

| 4         | RF_N                               | RF I/O     | Negative RF input signal to LNA in RX mode.<br>Negative RF output signal from PA in TX mode.<br>It should be biased by AVDD_DCPL1. Refer to Figure 2<br>(Sec.5). |  |  |  |

| 6         | RBIAS                              | Analog I/O | External precision bias resistor (510K) to generate the reference current.                                                                                       |  |  |  |

| 25        | XOSCO                              | Analog I/O | X-tal osc. buffer output or Crystal-unit pin-2                                                                                                                   |  |  |  |

| 26        | XOSCI                              | Analog I/O | X-tal osc. buffer input or Crystal-unit pin-1                                                                                                                    |  |  |  |

| 1         | AVDD1                              | Power I    | 1.8V to 3.6V RF/analog power supply connection                                                                                                                   |  |  |  |

| 28        | AVDD2                              | Power I    | 1.8V to 3.6V RF/analog power supply connection                                                                                                                   |  |  |  |

| 7         | AVDD3                              | Power I    | 1.8V to 3.6V RF/analog power supply connection                                                                                                                   |  |  |  |

| 5         | AVDD_DCPL1                         | Power O    | Regulated Output of AVDD1 for PA bias                                                                                                                            |  |  |  |

| 27        | AVDD_DCPL2                         | Power O    | Regulated Output of AVDD2 for decoupling                                                                                                                         |  |  |  |

| 8         | ATEST0                             | Analog O   | Analog Temperature sensor output<br>Analog test signal output                                                                                                    |  |  |  |

| 9         | ATEST1                             | Analog O   | Analog test signal output                                                                                                                                        |  |  |  |

| Digital   |                                    |            |                                                                                                                                                                  |  |  |  |

#### Table 1. MG2420 Pin Description

| Pin            | Pin Name | Pin type    | Pin Description                                                                           |

|----------------|----------|-------------|-------------------------------------------------------------------------------------------|

| 19             | SCLK     | Digital I   | SPI Interface: Serial Clock.                                                              |

| 18             | SO       | Digital O   | SPI Interface: Serial Out                                                                 |

| 17             | SI       | Digital I   | SPI Interface: Serial In                                                                  |

| 16             | CSn      | Digital I   | SPI Interface: Chip Select. Active low.                                                   |

| 20             | RESETB   | Digital I   | External reset. Active low.                                                               |

| 10             | P[0]     | Digital I/O |                                                                                           |

| 11             | P[1]     | Digital I/O | General purpose digital I/O.<br>Typical usage is setting to output mode to interface with |

| 12             | P[2]     | Digital I/O | MCU. When the SIGNAL OUT (0x2F6[6:4]) sets to 0x2,                                        |

| 13             | P[3]     | Digital I/O | P[0]~P[5] are assigned to TRSW, nTRSW, IRQ, CRCOK,                                        |

| 14             | P[4]     | Digital I/O | PLL_LOCK and EXTCLK, respectively; for details, refer to Sec.7.4 and Sec.9.3.             |

| 15             | P[5]     | Digital I/O | 366.7.4 and 366.9.3.                                                                      |

| 22             | DVREGEN  | Digital I   | Digital VREG enable input.<br>When high, digital voltage regulator is active.             |

| 24             | DVDD     | Power O     | Regulated Output of DVDD3V for decoupling                                                 |

| 23             | DVDD3V   | Power I     | 1.8V to 3.6V digital power supply connection                                              |

| 21             | MS       | Digital I   | NC(Not Connected)                                                                         |

| Ground a       | nd NC    |             |                                                                                           |

| Pin            | Pin Name | Pin type    | Pin Description                                                                           |

| Exposed bottom | GND      | Ground      | Ground for RF, analog, digital core, and IO                                               |

| 3              | NC       |             | NC<br>It can be connected to GND.                                                         |

RF\_P and RF\_N are the differential RF input/output ports. The balun and impedance matching circuits are required to interface a single-ended 50-Ohm antenna.

There are 4 pins connected to 3.0V supply, which is applied to internal voltage regulators. And there are 3 output pins of the regulated 1.2V voltages for decoupling. These regulated outputs should not be used to supply power to external circuits. DVDD is the output of the internal digital regulator which is controlled by the DVREGEN pin. Other analog voltage regulators are controlled by the power management block and activated by the power mode.

SCLK, SO, SI, and CSn are used in slave SPI interface. RESETB is an external reset input with active low.

The exposed die pad is located at the bottom of the chip and electrically connected to the die ground inside the package. It shall be soldered to the board ground.

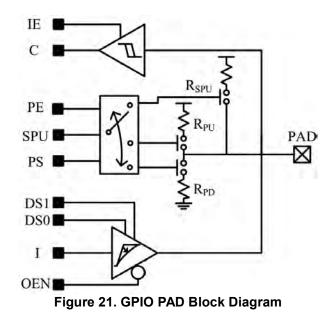

| Equivalent Circuit Schematic                                               | nt Circuit Summary<br>Reset Status | Note                                                                                                                              |

|----------------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| GPIO (P[5:0])                                                              |                                    |                                                                                                                                   |

| IE<br>C<br>PE<br>SPU<br>PS<br>DS1<br>DS0<br>I<br>OEN<br>OEN                | Input with pull-up                 | Refer to <u>Sec.7.4.</u><br>In Deep Sleep<br>Mode( DVREGEN =<br>Low), PAD Status is<br>Strong Pull-Up                             |

| SCLK, SI, CSn, RESETB                                                      | 1                                  | 1                                                                                                                                 |

| c PAD                                                                      | Input with HiZ                     | In Deep Sleep<br>Mode( DVREGEN =<br>Low), PAD Status is<br>Strong Pull-Up                                                         |

| MS                                                                         |                                    |                                                                                                                                   |

| C PAD                                                                      | Input with pull-down               | In Deep Sleep<br>Mode( DVREGEN =<br>Low), PAD Status is<br>Strong Pull-Up                                                         |

| SO                                                                         |                                    | 1                                                                                                                                 |

| IE<br>C<br>SPU<br>SPU<br>SPU<br>SPU<br>RSPU<br>RSPU<br>RSPU<br>RSPU<br>RSP | Input with pull-up                 | Output @ CSn=low<br>Otherwise, input with<br>pull-up<br>In Deep Sleep<br>Mode( DVREGEN =<br>Low), PAD Status is<br>Strong Pull-Up |

|                                                                            |                                    |                                                                                                                                   |

|                                                                            | Input                              |                                                                                                                                   |

| c PAD                                                                      |                                    |                                                                                                                                   |

#### Table 2. I/O Equivalent Circuit Summary

## 4. ELECTRICAL CHARACTERISTICS

### 4.1. Absolute Maximum Ratings

| Symbol            | Parameter                                  | Rating             | Unit |

|-------------------|--------------------------------------------|--------------------|------|

| V <sub>DDIO</sub> | Digital I/O supply voltage                 | -0.3 to 3.6        | V    |

| V <sub>DDA</sub>  | Analog supply voltage                      | -0.3 to 3.6        | V    |

| V <sub>DD12</sub> | Regulated output voltage on pins 5, 24, 27 | -0.3 to 1.32       | V    |

| T <sub>STG</sub>  | Storage Temperature                        | -40 to 150         | °C   |

| ESD               | HBM<br>MM<br>CDM                           | 2000<br>200<br>750 | V    |

Stress exceeding one or more of the limiting values may cause permanent damage to the device.

These are stress ratings only. And functional operation of the device at these or any other conditions beyond those indicated under "ELECTRICAL CHARACTERISTICS" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

**NOTE1:** All voltage values are based on  $V_{SS}$  and  $V_{SSIO}$ .

**NOTE2:** These values were obtained under worst-case test conditions specially prepared for MG2420 and these conditions are not sustained in normal operation environment.

**CAUTION:** ESD sensitive device. Precaution should be used when handling the device in order to prevent permanent damage.

### 4.2. Recommended Operating Conditions

| Symbol            | Parameter                              | MIN | TYP | MAX | Unit |

|-------------------|----------------------------------------|-----|-----|-----|------|

| V <sub>DDIO</sub> | Digital I/O supply voltage (DVDD3V)    | 1.8 | 3.0 | 3.6 | V    |

| V <sub>DDA</sub>  | Analog supply voltage on pins 1, 7, 28 | 1.8 | 3.0 | 3.6 | V    |

| T <sub>OP</sub>   | Operating temperature range            | -40 |     | 85  | °C   |

| Symbol            | Parameter                                | MIN  | TYP  | MAX  | Unit |

|-------------------|------------------------------------------|------|------|------|------|

| V <sub>DDIO</sub> | I/O supply voltage(DVDD3V)               | 1.8  | 3.0  | 3.6  | V    |

| AGND              | Chip ground                              |      | 0    |      | V    |

| V <sub>IH</sub>   | Input high voltage                       | 2.0  |      | 3.6  | V    |

| V <sub>IL</sub>   | Input low voltage                        | -0.3 |      | 0.8  | V    |

| V <sub>OH</sub>   | Output high voltage                      | 2.4  |      |      | V    |

| V <sub>OL</sub>   | Output low voltage                       |      |      | 0.4  | V    |

| R <sub>PU</sub>   | Pull-up Resistance                       |      | 66   |      | kΩ   |

| R <sub>PD</sub>   | Pull-down Resistance                     |      | 66   |      | kΩ   |

| R <sub>SPU</sub>  | Strong Pull-up Resistance<br>DVDD3V=3.3V | 1.42 | 1.62 | 1.92 | kΩ   |

### 4.3. Digital I/O DC Characteristics

### 4.4. Current Consumption

Test Conditions: T<sub>OP</sub>=25C, V<sub>DDA</sub>=V<sub>DDIO</sub>=3.0V,  $f_{RF}$ =2.45GHz, Data rate=250Kbps

| Parameter                                                                                                                                                                                                              | MIN | TYP                                                                          | MAX | UNIT | Note                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------|-----|------|------------------------------------------------------------------------------------|

| TX Mode<br>@+9dBm Output Power<br>@+8dBm Output Power<br>@+7dBm Output Power<br>@+6dBm Output Power<br>@+5dBm Output Power<br>@+3dBm Output Power<br>@+2dBm Output Power<br>@+1dBm Output Power<br>@ 0dBm Output Power |     | 28.4<br>24.7<br>22.1<br>21.1<br>20.5<br>19.1<br>18.5<br>17.4<br>16.4<br>16.1 |     | mA   | Measured at<br>2450MHz Channel<br>AES, Peripheral, and<br>Temp. Sensor<br>Disabled |

| RX Mode                                                                                                                                                                                                                |     | 15.4                                                                         |     | mA   | AES, Peripheral, and<br>Temp. Sensor<br>Disabled                                   |

| Deep Sleep Mode                                                                                                                                                                                                        |     |                                                                              | 1   | μA   | DVREGEN=0                                                                          |

| Analog Temperature Sensor                                                                                                                                                                                              |     | 0.06                                                                         |     | mA   | Current consumption increases at using this                                        |

### 4.5. RF Receive Section

#### 4.5.1. Chip Rate of 2Mcps (RF Bandwidth: 2MHz)

Test Conditions: T\_{OP}=25C, V\_{DDA}=V\_{DDIO}=3.0V, f\_{RF}=2.45GHz

| Parameter                                           | MIN  | TYP        | MAX  | UNIT | Note                                                                                                   |

|-----------------------------------------------------|------|------------|------|------|--------------------------------------------------------------------------------------------------------|

| RF Frequency Range<br>(Center Frequency)            | 2405 |            | 2480 | MHz  |                                                                                                        |

| Maximum Input Level<br>1000 kbps<br>250 kbps        |      | -3.7<br>-2 |      | dBm  | PER≤1%<br>Packet length of 20-byte                                                                     |

| Spurious Radiation<br>30-1000 MHz<br>1-12.75 GHz    |      | -60<br>-60 |      | dBm  | Compiles with EN 300 328,<br>EN 300 400, FCC, and ARIB<br>STD-T66.                                     |

| Received RF Bandwidth<br>(Chip Rate)                |      | 2          |      | MHz  |                                                                                                        |

| Channel Spacing                                     |      | 5          |      | MHz  | Compiles with IEEE<br>802.15.4                                                                         |

| Receiver Sensitivity<br>1000 kbps<br>250 kbps       |      | -93<br>-97 |      | dBm  | PER≤1%<br>Packet length of 20-byte                                                                     |

| Adjacent Channel<br>Rejection<br>+5MHz<br>-5MHz     |      | 30<br>31   |      | dB   | 250kbps, 20-byte<br>P <sub>RF</sub> = sensitivity+3<br>Non-Filtered IEEE 802.15.4<br>interferer signal |

| Adjacent Channel<br>Rejection<br>+5MHz<br>-5MHz     |      | 48<br>49   |      | dB   | 250kbps, 20-byte<br>P <sub>RF</sub> = sensitivity+3<br>Filtered IEEE 802.15.4<br>interferer signal     |

| Alternate Channel<br>Rejection<br>+10MHz<br>-10MHz  |      | 53<br>56   |      | dB   | 250kbps, 20-byte<br>P <sub>RF</sub> = sensitivity+3<br>Non-Filtered IEEE 802.15.4<br>interferer signal |

| Alternate Channel<br>Rejection<br>+10MHz<br>-10MHz  |      | 58<br>59   |      | dB   | 250kbps, 20-byte<br>P <sub>RF</sub> = sensitivity+3<br>Filtered IEEE 802.15.4<br>interferer signal     |

| Others Channel<br>Rejection<br>≥ +15MHz<br>≥ -15MHz |      | 65<br>65   |      | dB   | 250kbps, 20-byte<br>P <sub>RF</sub> = sensitivity+3<br>Non-Filtered IEEE 802.15.4<br>interferer signal |

| Co-channel Rejection                                |      | -6.6       |      | dB   | 250kbps, 20-byte<br>P <sub>RF</sub> = sensitivity+3<br>Non-Filtered IEEE 802.15.4<br>interferer signal |

| Wi-Fi IEEE 802.11n<br>Rejection                     |      | 47         |      | dB   | 250Kbps, 40-byte<br>WANTED Signal -82dBm,<br>Interference 802.11n<br>(BW40MHz) +27/-27Mhz              |

| Blocking/desensitization<br>-250MHz<br>-100MHz<br>-50MHz<br>+50MHz<br>+100MHz<br>+250MHz | -20<br>-23<br>-23<br>-25<br>-23<br>-23<br>-23 | dBm | 250kbps, 20-byte<br>P <sub>RF</sub> = sensitivity+3<br>ETSI EN 300 440-1 V1.6.1<br>(2010-04)-37[2]<br>blocking/desensitization |

|------------------------------------------------------------------------------------------|-----------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------|-----------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------|

#### 4.5.2. Chip Rate of 4Mcps (RF Bandwidth: 4MHz)

Test Conditions: T\_{OP}=25C, V\_{DDA}=V\_{DDIO}=3.0V, f\_{RF}=2.45GHz

| Parameter                                           | MIN  | TYP         | MAX  | UNIT | Note                                                                                                 |

|-----------------------------------------------------|------|-------------|------|------|------------------------------------------------------------------------------------------------------|

| RF Frequency Range<br>(Center Frequency)            | 2405 |             | 2480 | MHz  |                                                                                                      |

| Maximum Input Level<br>3000 kbps<br>2000 kbps       |      | 2.3<br>-0.2 |      | dBm  | PER≤1%<br>Packet length of 20-byte                                                                   |

| Spurious Radiation<br>30-1000 MHz<br>1-12.75 GHz    |      | -60<br>-60  |      | dBm  | Compiles with EN 300 328,<br>EN 300 400, FCC, and ARIB<br>STD-T66.                                   |

| Received RF Bandwidth<br>(Chip Rate)                |      | 4           |      | MHz  |                                                                                                      |

| Channel Spacing                                     |      | 10          |      | MHz  | Recommended.                                                                                         |

| Receiver Sensitivity<br>3000 kbps<br>2000 kbps      |      | -86<br>-90  |      | dBm  | PER≤1%<br>Packet length of 20-byte                                                                   |

| Adjacent Channel<br>Rejection<br>+10MHz<br>-10MHz   |      | 41<br>41    |      | dB   | 2Mbps, 20-byte<br>P <sub>RF</sub> = sensitivity+3<br>Non-Filtered IEEE 802.15.4<br>interferer signal |

| Alternate Channel<br>Rejection<br>+20MHz<br>-20MHz  |      | 60<br>61    |      | dB   | 2Mbps, 20-byte<br>P <sub>RF</sub> = sensitivity+3<br>Non-Filtered IEEE 802.15.4<br>interferer signal |

| Others Channel<br>Rejection<br>≥ +30MHz<br>≥ -30MHz |      | 61<br>62    |      | dB   | 2Mbps, 20-byte<br>P <sub>RF</sub> = sensitivity+3<br>Non-Filtered IEEE 802.15.4<br>interferer signal |

| Co-channel Rejection                                |      | -6          |      | dB   | 2Mbps, 20-byte<br>P <sub>RF</sub> = sensitivity+3<br>Non-Filtered IEEE 802.15.4<br>interferer signal |

| Blocking/desensitization<br>-250MHz<br>-100MHz<br>-50MHz<br>+50MHz<br>+100MHz<br>+250MHz |  | -24<br>-28<br>-28<br>-29<br>-28<br>-27 |  | dBm | 2Mbps, 20-byte [2]<br>P <sub>RF</sub> = sensitivity+3 |

|------------------------------------------------------------------------------------------|--|----------------------------------------|--|-----|-------------------------------------------------------|

|------------------------------------------------------------------------------------------|--|----------------------------------------|--|-----|-------------------------------------------------------|

### 4.6. RF Transmit Section

#### 4.6.1. Chip Rate of 2Mcps (RF Bandwidth: 2MHz)

Test Conditions: T\_{OP}=25C, V\_{DDA}=V\_{DDIO}=3.0V, f\_{RF}=2.45GHz

| Parameter                                                                      | MIN        | ТҮР                      | MAX                                          | UNIT | Note                                                   |

|--------------------------------------------------------------------------------|------------|--------------------------|----------------------------------------------|------|--------------------------------------------------------|

| Transmit Chip Rate                                                             |            | 2                        |                                              | Mcps |                                                        |

| TX Output Power                                                                | 9 dBm reco |                          | Using the<br>recommended<br>matching circuit |      |                                                        |

| Error Vector Magnitude (EVM)                                                   |            | 6                        |                                              | %    |                                                        |

| Harmonics<br>2 <sup>nd</sup> harmonic<br>3 <sup>rd</sup> harmonic              |            | -45<br>-45               |                                              | dBm  | Using the recommended matching circuit                 |

| Spurious Emission<br>30Hz~1GHz<br>1GHz~2.5GHz<br>2.5GHz~12.7GHz<br>5.15~5.3GHz |            | -60<br>-60<br>-60<br>-60 |                                              | dBm  | Complies with EN 300<br>440, FCC, and ARIB<br>STD-T66. |

#### 4.6.2. Chip Rate of 4Mcps (RF Bandwidth: 4MHz)

Test Conditions:  $T_{OP}$ =25C,  $V_{DDA}$ = $V_{DDIO}$ =3.0V,  $f_{RF}$ =2.45GHz

| Parameter                                                                      | MIN | TYP                      | MAX | UNIT | Note                                                   |

|--------------------------------------------------------------------------------|-----|--------------------------|-----|------|--------------------------------------------------------|

| Transmit Chip Rate                                                             |     | 4                        |     | Mcps |                                                        |

| TX Output Power                                                                |     | 9                        |     | dBm  | Using the<br>recommended matching<br>circuit           |

| Error Vector Magnitude (EVM)                                                   |     | 8                        |     | %    |                                                        |

| Harmonics<br>2 <sup>nd</sup> harmonic<br>3 <sup>rd</sup> harmonic              |     | -45<br>-45               |     | dBm  | Using the recommended matching circuit                 |

| Spurious Emission<br>30Hz~1GHz<br>1GHz~2.5GHz<br>2.5GHz~12.7GHz<br>5.15~5.3GHz |     | -60<br>-60<br>-60<br>-60 |     | dBm  | Complies with EN 300<br>440, FCC, and ARIB<br>STD-T66. |

## 4.7. Frequency Synthesizer Characteristics

Test Conditions: T<sub>OP</sub>=25C, V<sub>DDA</sub>=V<sub>DDIO</sub>=3.0V,  $f_{RF}$ =2.45GHz

| Parameter                                                                                                            | MIN | ТҮР                                                     | MAX | UNIT   | Note |

|----------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------|-----|--------|------|

| Phase Noise<br>@ 100KHz offset<br>@ 1MHz offset<br>@ 2MHz offset<br>@ 3MHz offset<br>@ 5MHz offset<br>@ 10MHz offset |     | -82.2<br>-110.3<br>-117.0<br>-119.5<br>-123.3<br>-134.0 |     | dBc/Hz |      |

| @ 50MHz offset                                                                                                       |     | -149.0                                                  |     |        |      |

| PLL Lock Time                                                                                                        |     |                                                         | 80  | μsec   |      |

## 4.8. Crystal Oscillator

| Parameter                                    | MIN | TYP             | MAX             | UNIT | Note |

|----------------------------------------------|-----|-----------------|-----------------|------|------|

| Crystal Oscillator Frequency                 |     | 32              |                 | MHz  |      |

| Crystal Frequency Accuracy<br>Requirement -4 |     |                 | +40             | ppm  |      |

| Equivalent series resistance (ESR)           |     | 30 <sup>1</sup> | 60 <sup>2</sup> | Ω    |      |

| Crystal shunt capacitance (C <sub>0</sub> )  |     | 3               | 5               | pF   |      |

| Crystal load capacitance (CL)                |     | 9 <sup>1</sup>  | 13 <sup>2</sup> | pF   |      |

| Start-up time                                |     |                 | 0.8             | ms   |      |

## 4.9. Analog Temperature Sensor

Test Conditions:  $V_{DDA}=V_{DDIO}=3.0V$

| Parameter               | MIN | TYP     | MAX | UNIT  | Note                                |

|-------------------------|-----|---------|-----|-------|-------------------------------------|

| Output voltage at -40°C |     | 0.8276  |     | V     |                                     |

| Output voltage at 0°C   |     | 0.7709  |     | V     |                                     |

| Output voltage at +27°C |     | 0.7322  |     | V     |                                     |

| Output voltage at +85°C |     | 0.6463  |     | V     |                                     |

| Temperature coefficient |     | -1.4526 |     | mV/°C | Linear fitted from<br>-40°C to 85°C |

| Current consumption     |     | 0.06    |     | mA    |                                     |

<sup>&</sup>lt;sup>1</sup> The negative resistance of driving circuit is five times larger than the ESR of crystal oscillator with crystal satisfying above TYP conditions.

<sup>&</sup>lt;sup>2</sup> The negative resistance of driving circuit is two times larger than the ESR of crystal oscillator with crystal satisfying above MAX conditions.

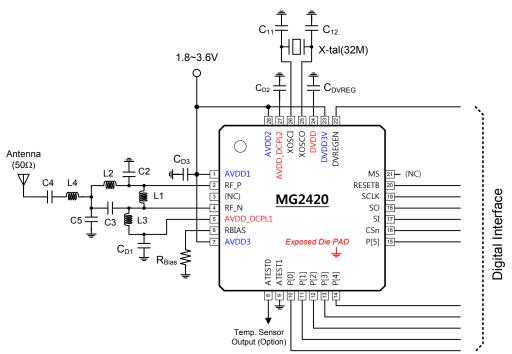

## 5. APPLICATION

A typical application diagram of MG2420 is shown in [Figure 2]. A few external components are required as shown in the figure. [Table 3] describes the external components and lists their typical values.

The inductor, L1 is used as an RF matching and as an output load of the PA(power amplifier) simultaneously. The components near the RF\_P/RF\_N pins, L2, L3, C2, and C3 form a balun which converts the differential RF signals to a single-ended RF signal. L4, C4, and C5 form an LC harmonic filter to suppress the TX output harmonics. In addition, C4 is used for DC blocking. All together with adequate values, they also transform the impedance to match a 50-Ohm antenna.

As shown in [Figure 2], RF\_P and RF\_N are biased by AVDD\_DCPL1 through L1 and L3.

The 32MHz crystal with loading capacitors is connected to MG2420. It provides the reference frequency source for MG2420.

CD1, CD2, and CD3 are supply decoupling capacitors, whose values depend on PCB artwork and stack-up information.

Figure 2. MG2420 Application Circuit

| No | Component          | Description                                                      | Value                 |

|----|--------------------|------------------------------------------------------------------|-----------------------|

| 1  | L1                 | RF matching inductor                                             | 5.1nH                 |

| 2  | L2, L3             | RF balun inductors                                               | 2.4nH                 |

| 3  | C2                 | RF balun capacitor                                               | 1.2pF                 |

| 4  | C3                 | RF balun capacitor                                               | 1.0pF                 |

| 5  | L4                 | RF LC filter/matching inductor                                   | 3.9nH                 |

| 6  | C5                 | RF LC filter/matching capacitor                                  | 1.5pF                 |

| 7  | C4                 | DC blocking capacitor                                            | 1.0pF                 |

| 8  | Rbias              | Resistor for internal bias current reference                     | 510KΩ                 |

| 9  | X-tal              | 32MHz crystal unit                                               | 32M<br>(±40ppm, 16pF) |

| 10 | C11, C12           | Crystal loading capacitors                                       | 13pF <sup>3</sup>     |

| 11 | C <sub>DVREG</sub> | Decoupling capacitor for DVDD (digital voltage regulator output) | 1uF                   |

| 12 | C <sub>D1</sub>    | Decoupling capacitor for AVDD_DCPL1                              | 1nF                   |

| 13 | C <sub>D2</sub>    | Decoupling capacitor for AVDD_DCPL2                              | 1uF                   |

| 14 | C <sub>D3</sub>    | Decoupling capacitor for AVDD1                                   | 1uF                   |

Table 3. Bill of Materials for Figure 2

<sup>&</sup>lt;sup>3</sup> The value of crystal loading capacitance depends on crystal oscillator.

## 6. FUNCTIONAL DESCRIPTION

### 6.1. Block Diagram

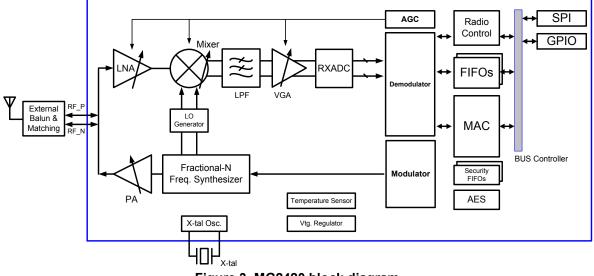

Figure 3. MG2420 block diagram.

A simplified block diagram of MG2420 is shown in [Figure 3]. Since the bidirectional differential RF pins are used for RX and TX, no external T/R switch is required. The receiver is designed with direct-conversion architecture, and it operates in the 2.4GHz band with excellent receiver sensitivity and robustness to interference. Transmitter architecture is based on direct-modulation technique using direct RF frequency synthesis.

The LNA amplifies the received RF signal at RF\_P and RF\_N pins, and the RX Mixer converts the RF signal to the baseband frequency in quadrature(I and Q). Gains of LNA and mixer are controlled coarsely by AGC block.

Channel filtering occurs in the LPF(low-pass filter). The VGA(variable-gain amplifier) provides sufficient gain, controlled by the AGC, to drive the RXADC(analog-to-digital converter). And, the RX ADC converts the VGA output signals to the signed binary digital signals.

The frequency synthesizer (PLL) generates the carrier signals for channel frequency.

The LO generator transforms the differential outputs of the PLL into the quadrature(I, Q) signals required for local signals in the RX Mixer.

The PA(power amplifier) amplifies the modulated RF signal from the PLL. TX output power level is controlled in the PA by register setting.

The modulator transforms the raw data came from TX FIFO into the modulated signals. It consists of the bit-to-symbol mapping block, the spreading block, the convolution encoder, the interleaver, and the mapping circuit for direct-modulation.

The demodulator processes the digitized RX signals of the ADC outputs, which store the RX

FIFO after processing correlation, frequency offset control, timing synchronization, deinterleaver, and viterbi decoder.

The AGC(automatic gain controller) controls gains of RF circuits to maintain the input level of the RXADC.

The functions of the MAC are to transfer the data from higher layer to PHY block, to send the received data from PHY to higher layer, and to encrypt/decrypt the data in the AES.

The Radio Controller module controls the operation state, the FIFOs, power up/down of RF/Analog blocks, and clock on/off of modem sub blocks. It provides operating sequences for both transmit and receive. Also it controls the sleep mode.

The X-tal oscillator generates a reference clock for RF and digital blocks.

Several voltage regulators are integrated to provide the operating voltage for analog and digital blocks.

An SPI serial interface is used for radio configuration and packet handling. GPIO pins are typically used for microcontroller interface.

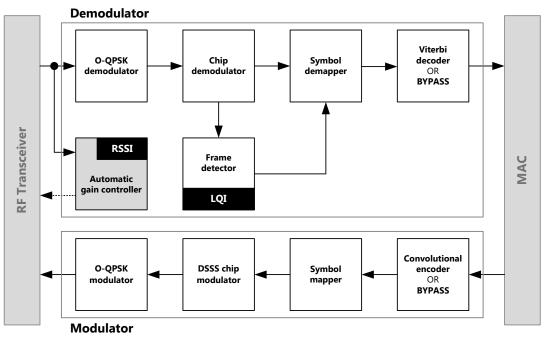

Figure 4. Baseband PHY block diagram

The baseband PHY (i.e. modem) is composed of the O-QPSK modulator and demodulator with simple convolutional channel coder. [Figure 4] shows the baseband PHY block diagram.

The modulation starts from fetching the data in the TX MAC FIFO. The PHY payload (PHY service data unit; PSDU) is optionally encoded with the convolutional channel encoder. After appending the preamble, SFD and length field to the PHY payload, a constructed frame (PHY protocol data unit; PPDU) is mapped to designated symbols according to the data-rate

control of the PHY controller. Each symbol is spread accordingly by the DSSS chip modulator. The spread PHY bit stream in the chip-level is then modulated to the O-QPSK signal and transmitted by the RF transmitter. Especially for the 250Kbps data-rate packet, its structure is fully compliant to the IEEE802.15.4 O-QPSK PHY specification.

With the RF receiver, the received O-QPSK signal is demodulated to the chip sequences. The gain amplifying blocks in the RF receiver are controlled by the automatic gain controller (AGC). The chip sequence is appropriately de-spread by the chip demodulator, and then the start of the designated frame is determined by detecting the synchronization header (preamble and SFD). When the SFD is detected, the baseband PHY generates the interrupt which indicates the start of a packet.

The length and the PHY payload followed by the synchronization header are decoded by the symbol demapper and Viterbi decoder (if the convolutional encoding is applied), and stored in the RX MAC FIFO. When the last data of the PHY payload is stored, the interrupt is generated to indicate the end of the packet reception. After a packet reception interrupt occurs, the RX MAC procedure is performed.

When a packet is received, the baseband PHY provides both of the received signal strength Indicator (RSSI) and the link quality indicator (LQI) automatically. They are used to decide the quality of the communication channel.

While a packet does not exist, the baseband PHY continuously provides the RSSI of the RF signal at antenna. The measured RSSI is used to decide the communication channel state. Clear channel assessment (CCA) operation is based on this information. The CCA operation is used to prevent a collision when multiple users try to use a channel simultaneously. When a channel is determined as busy, packet transmission is deferred until the channel state changes to idle.

#### 6.2. Data Rate

MG2420 supports various data rates of 1~3Mbps for applications beyond IEEE 802.15.4 compliances.

The 1Mbps modes, which is listed in [Table 4], occupy 2MHz RF channel bandwidth which is same as the IEEE 802.15.4-2.4GHz 250Kbps standard mode.

The 2M~3Mbps modes, which are listed in [Table 5], occupy an RF channel bandwidth of 4MHz.

The high data rate modes of 1M~3Mbps use decreased spreading factor with the same preamble structure as 250Kbps. Also, they can use the FEC. The data rate is selected by writing to the registers: SEL\_TXDR (0x211[3:0]) and CLK\_SEL(0x2C6[1]).

| RF Bandwidth=2MHz (Chip Rate: 2Mcps) / CLK_SEL=1 |                              |     |                        |  |  |  |  |  |

|--------------------------------------------------|------------------------------|-----|------------------------|--|--|--|--|--|

| Data Rate                                        | Sensitivity SEL_TXDR Comment |     |                        |  |  |  |  |  |

| 1Mbps                                            | -93 dBm                      | 0x1 | Using 1/2 FEC          |  |  |  |  |  |

| 250Kbps                                          | -97 dBm                      | 0x6 | IEEE802.15.4 compliant |  |  |  |  |  |

Table 5. Data Rate Modes for 4Mcps (PER≤1%, Packet length of 20-byte)

| RF Bandwidth=4MHz (Chip Rate: 4Mcps) / CLK_SEL=0 |                                 |     |               |  |  |  |  |  |  |

|--------------------------------------------------|---------------------------------|-----|---------------|--|--|--|--|--|--|

| Data Rate                                        | te Sensitivity SEL_TXDR Comment |     |               |  |  |  |  |  |  |

| 3Mbps                                            | -86 dBm                         | 0x3 | Using 3/4 FEC |  |  |  |  |  |  |

| 2Mbps                                            | -90 dBm                         | 0x1 | Using 1/2 FEC |  |  |  |  |  |  |

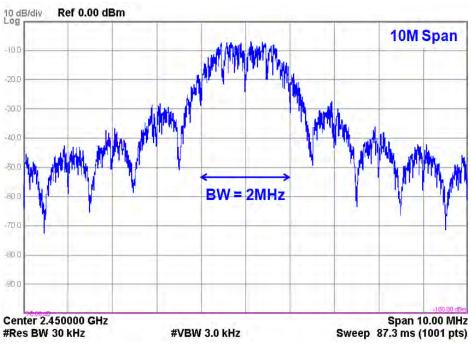

The modulated output spectrum for 2Mcps mode is shown in [Figure 5], and occupied RF bandwidth is 2MHz. The modulated output spectrum for 4Mcps mode is shown in [Figure 6]. For 4Mcps mode, occupied RF bandwidth is 4MHz.

Figure 5. Modulated signal spectrum for 2Mcps mode.

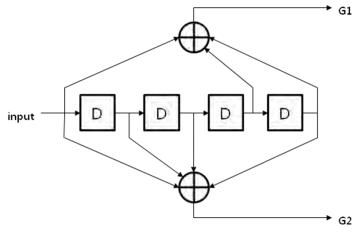

### 6.3. Forward Error Correction(FEC)

Especially for higher data rate modes, MG2420 provides the variable-rate convolutional channel coding for forward error correction (FEC). MG2420 supports the convolution coding with the rates of 1/2 and 3/4

As shown in [Figure 7], the convolutional encoder with the constraint length of 5 is used for the mother convolutional encoder with the rate of 1/2.  $G1(x) = x^4 + x + 1$ .  $G2(x) = x^4 + x^3 + x^2 + 1$ . The rates of 3/4 are available by puncturing of the output of the mother convolutional encoder as shown in [Table 6].

Figure 7. Convolutional encoder with rate of 1/2.

| Code Rate | Puncturing Matrix      | Transmitted Sequence    |

|-----------|------------------------|-------------------------|

| 1/2       | G1: 1<br>G2: 1         | G1[0] G2[0]             |

| 3/4       | G1: 1 0 1<br>G2: 1 1 0 | G1[0] G2[0] G2[1] G1[2] |

| Table | 6. | Puncturing | Pattern |

|-------|----|------------|---------|

|-------|----|------------|---------|

### 6.4. Packet Format

MG2420 supports multiple data rates ranged from 1Mbps to 3Mbps including 250Kbps. The data rate is selected by writing to the registers: SEL\_TXDR(0x211[3:0]) and CLK\_SEL(0x2C6[1]).

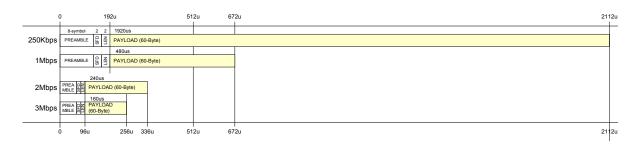

The packet format comparison for high data rates(≥250Kbps) with an example PAYLOAD length of 60-Byte is shown in [Figure 8]. The period of the preamble, SFD, and LEN for 1Mbps modes is the same for 250Kbps mode. Only PAYLOAD period is reduced. The total packet times for 2Mbps and 3Mbps modes become half compared to 1Mbps and 1.5Mbps modes respectively. Consequently, using high data rate modes leads to significant reduction of both communication time and power consumption.

The effective payload data rate is shown in [Figure 9]. Due to the overhead caused by the preamble, SFD, and length field, the effective data rate is lower than the configured data rate. Furthermore, the effective data throughput including the MAC overhead would be lowered further.

Figure 8. Packet format

Figure 9. Effective payload data rate. (a) 2Mcps mode. (b) 4Mcps mode.

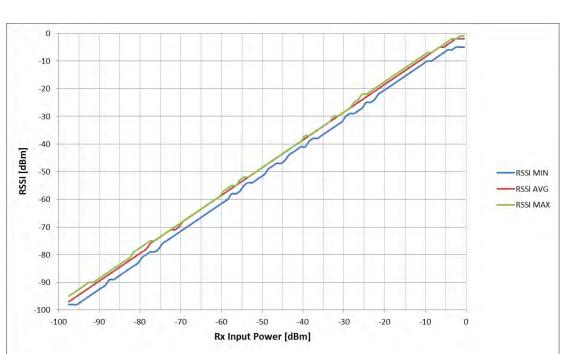

### 6.5. RSSI and Energy Detection

When a packet is received, a modem block automatically provides the Received Signal Strength Indicator(RSSI). RSSI is measured by averaging the power level of the received signal for a certain period. RSSI value is stored in a register and the stored value is kept until the new packet is received.

While a packet is not received, a modem block continuously provides the RF channel energy level at antenna. Measured energy level is used in order to decide the communication channel state.

As shown in [Table 7], RXENRG register indicates the averaged energy level of the received signal at antenna. Its value is a 2's complement integer in dBm. The PKTENRG register shows the energy level of the last received packet. Its value is retained until another packet is received.

A typical RSSI value as RX input power for 250kbps is shown in [Figure 10].

| Address<br>(hex) | Bit   | Name    | Reset<br>Value | R/W | Description                                                         |

|------------------|-------|---------|----------------|-----|---------------------------------------------------------------------|

| 0x274            | [7:0] | RXENRG  | 0x00           | R   | Averaged energy level of the received RF signal at antenna (in dBm) |

| 0x275            | [7:0] | PKTENRG | 0x00           | R   | Averaged energy level of the received packet (in dBm)               |

#### Table 7. RSSI measurement

| Table 8. RSSI Characteristics |                           |       |  |    |  |  |  |  |  |

|-------------------------------|---------------------------|-------|--|----|--|--|--|--|--|

| Parameter                     | ter MIN TYP MAX UNIT Note |       |  |    |  |  |  |  |  |

| RSSI Range                    |                           | 100   |  | dB |  |  |  |  |  |

| RSSI Accuracy                 |                           | +2/-4 |  | dB |  |  |  |  |  |

| Step Size                     |                           | 1     |  | dB |  |  |  |  |  |

Figure 10. Typical RSSI value vs. RX input power for 250kbps.

### 6.6. Clear Channel Assessment (CCA)

While a packet does not exist, the baseband PHY continuously provides the RF channel energy level at antenna. As described before, the measured energy level is used in order to decide the communication channel state. Clear channel assessment (CCA) operation is based on this information. The CCA operation is used in order to prevent a collision when multiple users try to use a channel simultaneously. When a channel is determined as busy, packet transmission is deferred until the channel state changes to idle.

The CCA operation is configured through the register (0x24C) as depicted in [Table 9].

| Address<br>(hex) | Bit   | Name       | Reset<br>Value |     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                   |

|------------------|-------|------------|----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x24C            | [7:6] | (Reserved) | 00             | R/W | Only '00' allowed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                   |

|                  | [5]   | CCA_FIX    | 1              | R/W | communication channe<br>CCA circuit in MG2420<br>a packet is not transmi<br>transmission regardles                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | tion channel state to idle. A<br>el state is determined by the<br>. When a channel state is busy<br>tted. This field allows packet<br>s of the channel state. When<br>e channel is always in idle |

|                  | [4:2] | (Reserved) | 000            | R/W | Only '000' allowed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                   |

|                  | [1:0] | CCAMD      | 00             | R/W | This field sets the method to determine the communication channel state. The following describes the three methods to detect the channel state.<br><u>Energy detection (ED)</u><br>This method determines the channel state as 'busy' when the energy of received signal is higher than the defined level.<br><u>Carrier detection (CD)</u><br>This method determines the channel state as 'busy' when an IEEE802.15.4 carrier is detected.<br><u>Frame detection (FD)</u><br>This method determines the channel state as 'busy' when an IEEE802.15.4 carrier is detected. |                                                                                                                                                                                                   |

|                  |       |            |                |     | CCAMD (binary)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Method                                                                                                                                                                                            |

|                  |       |            |                |     | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ED                                                                                                                                                                                                |

|                  |       |            |                |     | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CD                                                                                                                                                                                                |

|                  |       |            |                |     | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FD                                                                                                                                                                                                |

#### Table 9. CCA configuration

## 6.7. Link Quality Indicator (LQI)

When a packet is received, the baseband PHY provides both of the received signal strength Indicator (RSSI) and the link quality indicator (LQI). They are used in order to decide the quality of the communication channel.

MG2420 uses correlation results of multiple symbols in order to calculate an estimate of the LQI value. If LQI\_EN is "0x1", then LQI estimation is automatically performed for every received frame. LQI values are integers ranging from 0 to 255 as required by the IEEE 802.15.4 standard.

After receiving 8 first symbols following the SFD, MG2420 provides a correlation average value as an LQI. This is indicated by the LQI\_VALID register.

| Address<br>(hex) | Bit   | Name       | Reset<br>Value | R/W | Description                                 |

|------------------|-------|------------|----------------|-----|---------------------------------------------|

|                  | [7]   | LQI_VALID  | 0x0            | R   | LQI valid indicator                         |

| 0x26E            | [6:4] | (Reserved) | 0x0            | R/W | Only 0x0 allowed                            |

| UXZOE            | [3]   | LQI_EN     | 0x0            | R/W | LQI enable register (0: Disable, 1: Enable) |

|                  | [2:0] | (Reserved) | 0x0            | R/W | Only 0x0 allowed                            |

| 0x26F            | [7:0] | LQI        | 0x0            | R   | LQI value (0 ~ 255)                         |

#### 6.8. Integrated MAC

The integrated MAC block transmits the data received from high layer to baseband modem, or encrypts it and then transmits to baseband modem. In addition, it indicates the status of PHY and transmits the data received from baseband modem to high layer, or transmits the decrypted data to high layer.

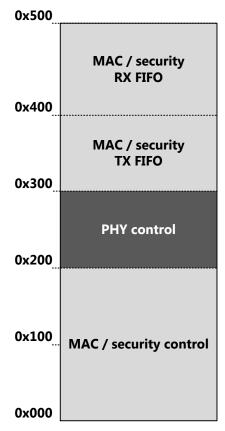

[Figure 11] shows the integrated MAC structure. The RX and TX FIFOs are separately implemented. The size of each FIFO is 256 bytes in order to process one IEEE802.15.4 packet along with buffering one packet. Each MAC FIFO is accessed through the dedicated FIFO access function of the SPI(Refer to <u>Sec 7.1.3</u>.). The MAC FIFO and security FIFO shares the address space and are distinguished by setting the register of SECMAP (0x19F).

Table 11] shows the address space of each FIFO.

When AUTO\_ACK (0x191) is set to '1', the ACK packet for the correctly received packet is automatically generated and sent.

[Table 12] describes general MAC/security control registers except for FIFO control registers.

Figure 11. Integrated MAC structure

| Table 11. MAO/Security 111 O Address Map |                       |     |                                                                                                           |  |  |  |  |

|------------------------------------------|-----------------------|-----|-----------------------------------------------------------------------------------------------------------|--|--|--|--|

| Address<br>(hex)                         | Name                  | R/W | Description                                                                                               |  |  |  |  |

| 0x300 ~ 0x3FF                            | MTXFIFO<br>or STXFIFO | R/W | Random access space for MAC TX FIFO (MTXFIFO;<br>SECMAP = 0)<br>or TX security FIFO (STXFIFO; SECMAP = 1) |  |  |  |  |

| 0x400 ~ 0x4FF                            | MRXFIFO<br>or SRXFIFO | R/W | Random access space for MAC RX FIFO (MRXFIFO;<br>SECMAP = 0)<br>or RX security FIFO (SRXFIFO; SECMAP = 1) |  |  |  |  |

#### Table 11. MAC/security FIFO Address Map

| Table 12. MAC/security control registers |         |           |                |                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                      |  |  |

|------------------------------------------|---------|-----------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Address<br>(hex)                         | Bit     | Name      | Reset<br>Value | R/W                                                                                                                                                                                                                                   | Description                                                                                                                                                                                                                          |  |  |

| 0x100 ~<br>0x10F                         | [127:0] | KEY0      |                | R/W                                                                                                                                                                                                                                   | 16-byte key (KEY0) for AES-128<br>0x10F: Most significant byte                                                                                                                                                                       |  |  |

| 0x110 ~<br>0x11C                         | [103:0] | RXNONCE   |                | R/W                                                                                                                                                                                                                                   | Used for decryption: 8-byte source address + 4-byte<br>frame counter + 1-byte key sequence counter<br>0x11C: Most significant byte of source address<br>0x114: Most significant byte of frame counter<br>0x110: Key sequence counter |  |  |

| 0x120 ~<br>0x12F                         | [127:0] | SAESBUF   |                | R/W                                                                                                                                                                                                                                   | Standalone encrypt/decrypt data buffer: After the AES-<br>128 operation, the result is stored in this register.<br>0x12F: Most significant byte of plain-text and<br>cipher-text                                                     |  |  |

| 0x130 ~<br>0x13F                         | [127:0] | KEY1      |                | R/W                                                                                                                                                                                                                                   | 16-byte key (KEY0) for AES-128<br>0x13F: Most significant byte                                                                                                                                                                       |  |  |

| 0x140 ~<br>0x14C                         | [103:0] | TXNONCE   |                | R/W Used for encryption: 8-byte source address + 4-l<br>frame counter + 1-byte key sequence counter<br>0x14C: Most significant byte of source address<br>0x144: Most significant byte of frame counter<br>0x140: Key sequence counter |                                                                                                                                                                                                                                      |  |  |

| 0x150 ~<br>0x157                         | [63:0]  | IEEE_ADDR |                | R/W                                                                                                                                                                                                                                   | 64-bit IEEE address<br>0x157: Most significant byte                                                                                                                                                                                  |  |  |

| 0x158 ~<br>0x159                         | [15:0]  | PAN_ID    |                | R/W                                                                                                                                                                                                                                   | 16-bit PAN ID<br>0x159: Most significant byte                                                                                                                                                                                        |  |  |

#### Table 12. MAC/security control registers